Using gate drivers to improve GaN performance in space-grade power converters

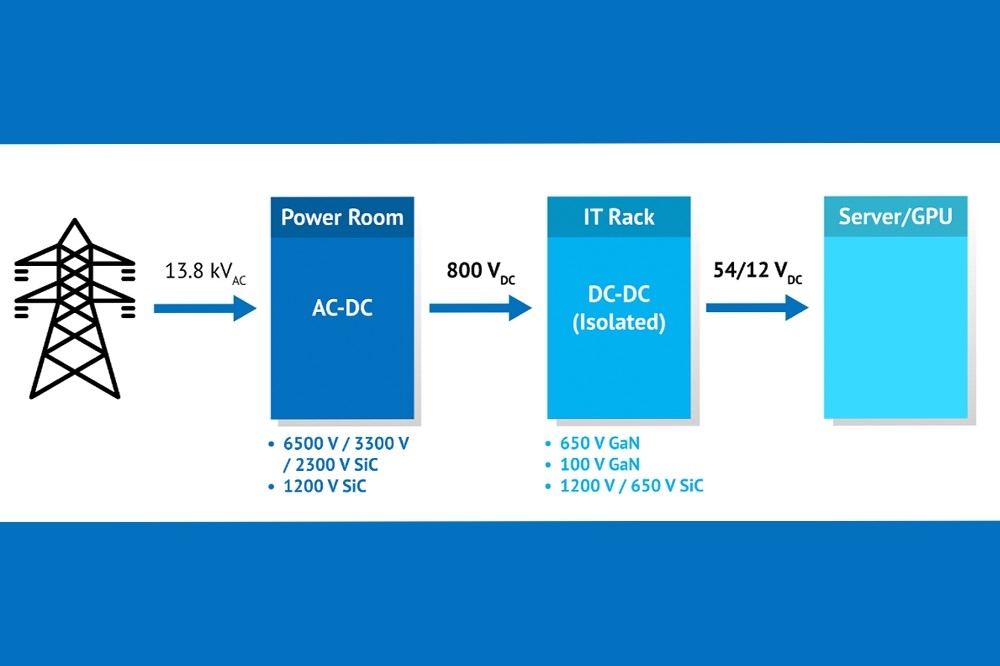

Using gallium nitride (GaN) field-effect transistors (FETs) in a power supply can help boost efficiency and enable operation at higher switching frequencies, helping designers meet the strict power requirements in space-grade radiation-tolerant and radiation-hardened applications.

BY John Dorosa, Systems Engineer, Power Design Services, TEXAS INSTRUMENTS

While the functionality as a switching element is common between silicon and GaN FETs, their gate drive characteristics differ enough to require specific driver components. The internal low-dropout regulators (LDOs), split-gate outputs and adjustable dead-time control in the Texas Instruments (TI) half-bridge GaN FET gate drivers like the TPS7H60003-SP and TPS7H6015-SEP enable power converters to extract more performance out of GaN FETs in a power supply. In this article, I’ll describe the parameters for using the gate drivers in GaN-based applications and highlight design recommendations at the system, schematic and printed circuit board (PCB) level.

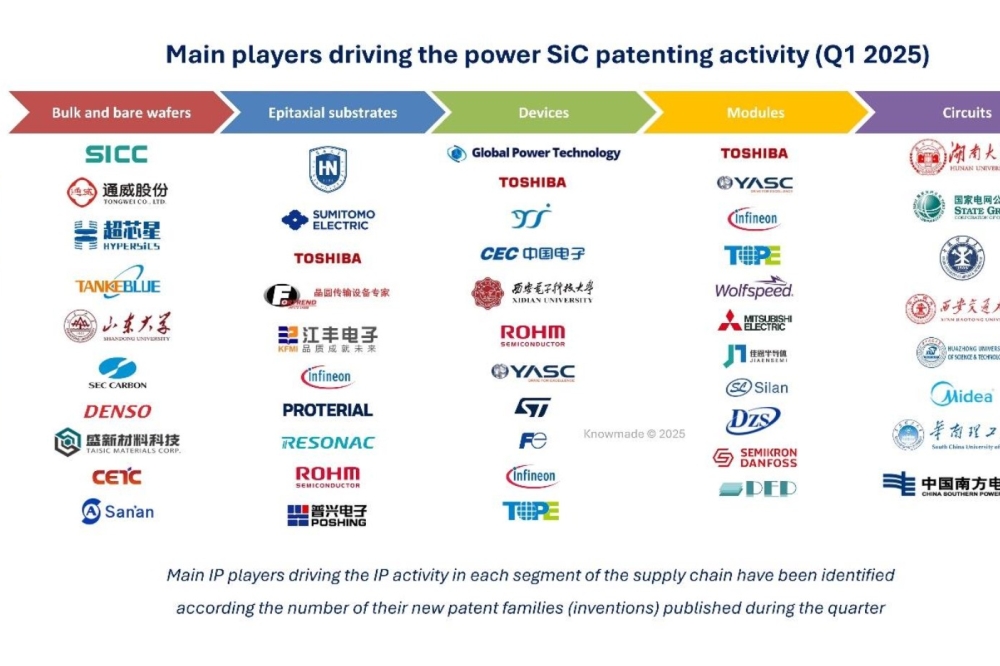

Figure 1. The TPS7H60xx-SP and TPS7H60xxSEP contain two die connected by a pair of communication capacitors.

Half-bridge GaN FET gate driver

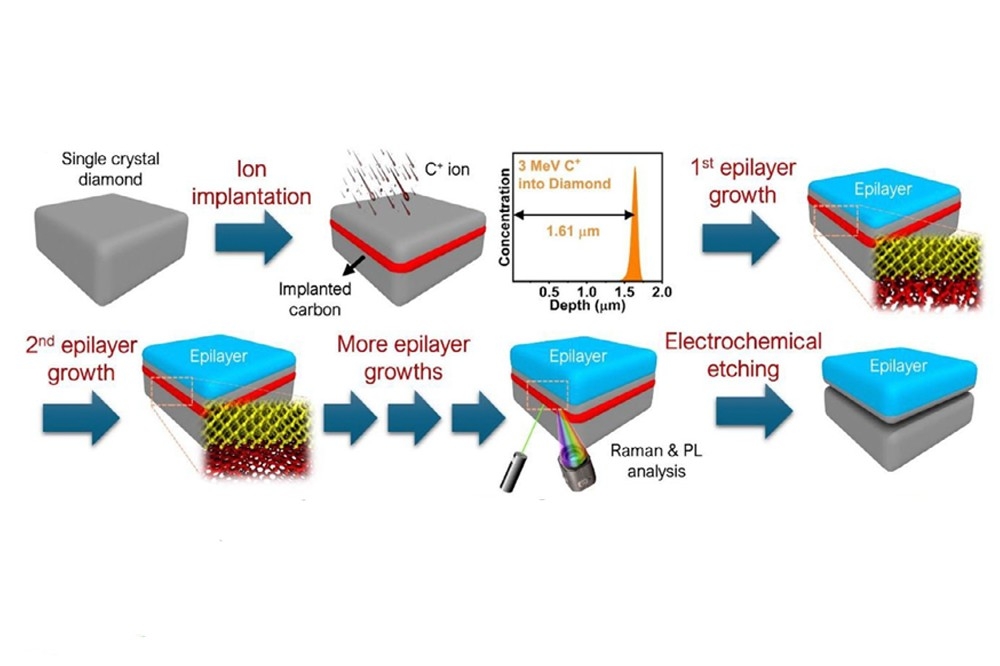

Devices in the TPS7H60xx-SP and TPS7H60xxSEP family have compelling total ionizing dose (TID) and single-event effect (SEE) performance, including validation of no cross-conduction events under single-event transient (SET) radiation. The half-bridge gate driver is constructed with two dies: a low-side gate driver and a high-side gate driver.

The low-side die contains blocks for logic, local biasing through an LDO, and a gate driver referenced to the PGND pins, while the high-side die has a local bias and gate driver referenced to the PSW pins (see Figure 1). The only connection between the two die are a pair of AC capacitors used to level-shift timing information from the low-side die to the high-side die. The 22V, 60V and 200V versions of the gate driver device correlate with the maximum stress that can be placed on the AC capacitors used for communication between the low- and high-side die [1].

Figure 2. Connecting the high-side gate driver to the switch node for a half-bridge configuration.

Topology selection

Having two independent gate-driver die enables you to use the device in a variety of power-converter topologies. The first option is a half-bridge configuration, where the low- and high-side gate drivers drive a stacked pair of metal-oxide semiconductor field-effect transistors (see Figure 2). In this configuration, the PSW pins connect to the switch node of the FET pair.

To ensure safe operation, the bus voltage must be lower than the voltage rating of the device chosen. An external supply is needed to bias the low-side gate driver. A bootstrap diode can bias the high-side gate driver; see Section 8.3.3 [1]. Common use cases include a synchronous buck converter for non-isolated topologies and primary FETs in a full-bridge converter for isolated topologies (see Figure 3).

Another option is to tie both the PSW and PGND pins to system ground and use the drivers as two low-side gate drivers (see Figure 4). In this case, the same external supply can bias the low- and high-side gate driver. You can use any voltage rating for driving dual low-side FETs with a shared ground because there is no potential between the PSW and PGND pins.

Figure 3. The half-bridge driver in non-isolated (a) and isolated topologies(b).

It is possible to use this approach to drive two phases of an interleaved boost converter for non-isolated applications. For isolated designs, this method is popular for driving the primary FETs of a push-pull converter and can also drive the synchronous rectifiers in any forward-derived topology (see Figure 5 a and b).

The last implementation is to use the high-side gate driver as a pseudo-isolated gate driver that can handle as much as 200V isolation between the two die within the device. For these applications, bootstrapping is not possible; instead, biasing the high-side gate driver will require an isolated external supply (see Figure 6).

You can use a functionally isolated high-side driver on the primary side of a two-switch flyback topology. Another use case is to drive a synchronous rectifier in a single-switch isolated topology, such as a synchronous flyback converter (see Figure 7). In this configuration, the isolation voltage is limited to the voltage rating of the device; however, in many space applications that is enough to meet isolation requirements.

Figure 4. Using the half-bridge device as a dual low-side gate driver simplifies connections.

Internal LDOs

Each die of half-bridge driver uses an integrated LDO regulator to bias the pullup voltage for its gate driver. Since the gate-to-source threshold voltages tend to be more sensitive for GaN (more than silicon) this feature ensures a clean 5V to drive the FETs for a given power stage.

I recommended using an external supply between 10V and 14V for the low-side die. The high-side die can handle a slightly wider 8V and 14V input. The recommended value will provide enough dropout voltage for the gate-driver stages. Additionally, the low-side die needs a slightly higher voltage because the logic portion runs off a separate LDO that creates a 7V bias.

Using LDOs will filter out noise from an external bias. The external bias comes from a flyback converter with a measured 8.72V peak-to-peak ripple voltage (see Figure 8). Regardless of the noise present, the LDO generates a bias with a 560mV peak-to-peak voltage, resulting in a notably cleaned up gate-drive signal to ensure proper driving of the GaN FET.

Figure 5. There are many uses for dual low-side gate drivers.

Adjustable dead-time control

In a half-bridge configuration, the time duration between one gate driver’s falling edge and the other gate driver’s rising edge has a major impact on total conversion efficiency. While operating in independent input mode, the controller determines this timing. In this use case, I recommended using interlock prevention while in independent input mode to prevent driving both FETs at the same time, which would result in a shoot-through event.

Another option is to use pulse-width modulation mode, where a single input signal controls the timing of both drive signals. Section 8.3.6 of the device data sheet [1] has instructions for tuning the dead time between the falling and rising edges.

Having too much dead time leads to increased power losses. For example, in a synchronous buck converter, the freewheeling current will conduct through the low-side FET before the gate-drive signal is applied. This issue is amplified with GaN FETs which do not have a body diode, leading to this portion of time being very lossy [2]. When optimizing a design, you should reduce the dead time to minimize losses.

Figure 6. The high-side gate driver in functionally isolated applications.

A dead time that is too short risks a shoot-through event. Even with the half-bridge gate driver preventing such effects, it is possible for one of the FETs to accidentally turn back on if the gate voltage is high enough (see Figure 9). This is especially important with GaN FETs, since their low gate-to-source voltage thresholds are susceptible to noise.

Extending the dead time will ensure that the gate signal from one gate driver is completely low before the other starts its rise time (see Figure 10). I recommended testing the actual timing by operating the controller in open loop before applying the input voltage.

Figure 7. Isolating the high-side gate driver can enable the use of higher-efficiency topologies.

Split-gate outputs

Each die of the half-bridge driver uses split-gate outputs to drive the FET high or low. This enables individual tuning of the rise and fall times with the series gate resistors, providing a simpler solution compared to a conventional totem-pole output driver, which requires an additional diode to achieve the same functionality (see Figure 11) [3]. Faster transition times are necessary for power converters to operate at high switching frequencies. The transition period during rise and fall times is inefficient for power conversion; therefore, it’s important to minimize the amount of time in this mode as much as possible.

Figure 8. An LDO cleaning up the ripple voltage from the external supply.

The total power losses in a GaN FET comprise conduction, output capacitance, third-quadrant and switching losses. Conduction and output capacitance losses depend heavily on the parameters for the FET chosen, and as I mentioned earlier, adjusting the dead time can optimize third-quadrant losses. The performance of the gate driver will have the most impact on the switching-loss portion of a FET’s total power losses [4]. See figure 12 for nominal voltage and current stress waveforms on a high-side FET in a buck Converter. Equation 1 calculates the switching losses [5]:Pswitching = VDS × fswitch / 2 × (trise × IFET, min + tfall × IFET, max) (1) where trise is the rise time of the FET and tfall is the fall time of the FET.

Figure 9. Too short of a dead-time delay may lead to a shoot-through event.

Speeding up the transition time will minimize switching losses; however, faster transitions can cause increased ringing on the switch node at the transition times. This is especially the case with GaN FETs, which tend to have lower gate capacitance compared to silicon FETs. Having control over both the rise and fall times enables you to optimize efficiency while keeping ringing at an acceptable amount for a given design.

PCB design considerations

The performance of any power supply that uses GaN FETs depends heavily on the quality of its PCB design. This is because of the very fast switching times, which make even small parasitic inductances significant. Section 9.4 of the datasheet [1] includes a full list of PCB recommendations and layout examples, but in this article, I will show the direct impact of minimizing parasitic inductance.

Figure 10: Extending the dead time ensures that the opposite gate drive has reached 0V.

A short path from the gate-driver output to the gate of the FET, returning through the source, is the first loop to consider. Additional inductance in this path may result in slower rise and fall times, leading to increased switching losses. In extreme cases, parasitic inductance may weaken the drive signal to the point that it cannot completely switch the FETs on and off. An initial revision of a synchronous buck converter included specific intent to keep the gate loop small (see Figure 13). While the gate-drive signals were clean for the high- and low-side FETs, there is noticeable ring on the switch node (see Figure 14).

Figure 11. A split-gate output gate driver (a) does not require an additional diode compared to totem-pole (b) output.

The second path to consider is the return path from the source of the low-side FET to the drain of the high-side FET through the input capacitor. In the initial PCB design, the input capacitors were placed far from the source of the low-side FET, which created enough inductance in the power stage to generate large amounts of switch-node ringing.

Figure 12. High-side voltage and current stresses in a synchronous buck converter.

Using the same bill of materials, another PCB minimizes the return path of the power stage (see Figure 15). Note that in this revision, the smallest ceramic capacitors are toward the middle of the capacitor banks instead of being lined up from largest to smallest. This layout technique, along with using the second layer for a return path, minimizes parasitic inductance, greatly improving switch-node performance (see Figure 16).

Figure 13. A buck converter PCB design with a minimized gate path.

Parasitic inductance is inevitable when creating a PCB design; however, the placement of components dictates where the inductance is in the circuit. Adding inductance to a gate-drive path runs the risk of not driving the FETs effectively, which could have implications on total conversion efficiency.

In this case, adding some gate inductance enabled a reduction in the power-path loop, greatly improving the switch-node ringing without having to change the selected components. With GaN-based power supplies, it’s important to design the PCB carefully to weigh the impact of parasitic inductance.

Figure 14. Large switch-node ringing on a synchronous buck-converter design.

Figure 15. Increasing the gate-drive path to enable better input-capacitor placement.

Figure 16. Reduced ringing time and total voltage stress on the switch node.

Conclusion

Using GaN FETs for power converters provides many benefits in space applications. Switching at higher frequencies becomes possible while also maintaining high conversion efficiency.

These attributes reduce overall solution size, weight and cost which helps a satellite meet the strict requirements for space missions. Higher switching frequencies are possible when partnering GaN FETs with the right gate driver.

TI optimized the feature set in the TPS7H60xx-SP and TPS7H60xxSEP family of half-bridge gate drivers for GaN FETs to help you get the most out of your next power-converter design.