Silvaco and Fraunhofer ISIT collaborate on GaN chip design

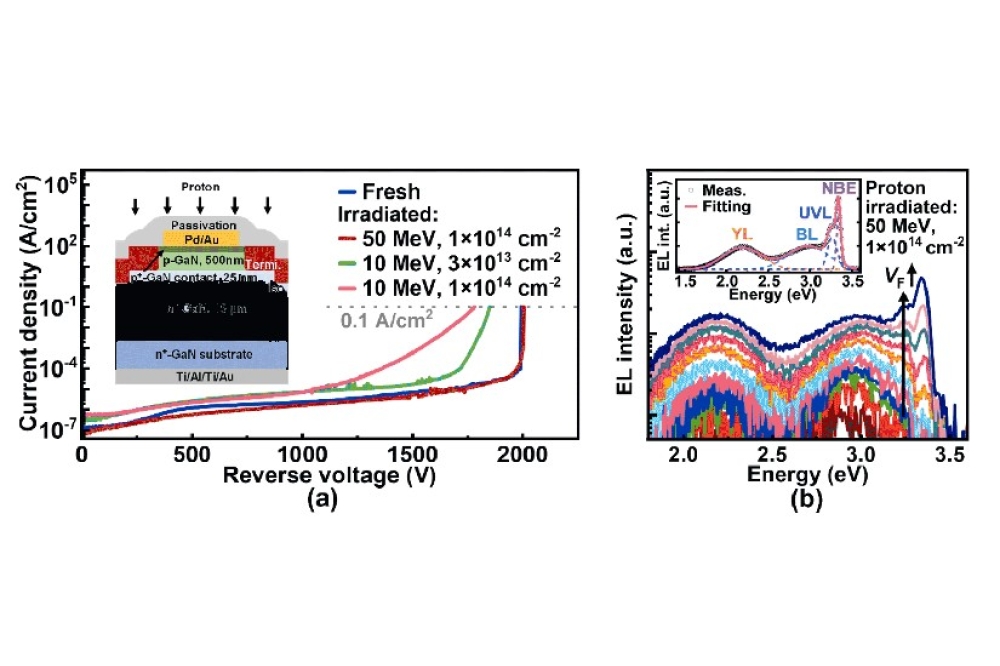

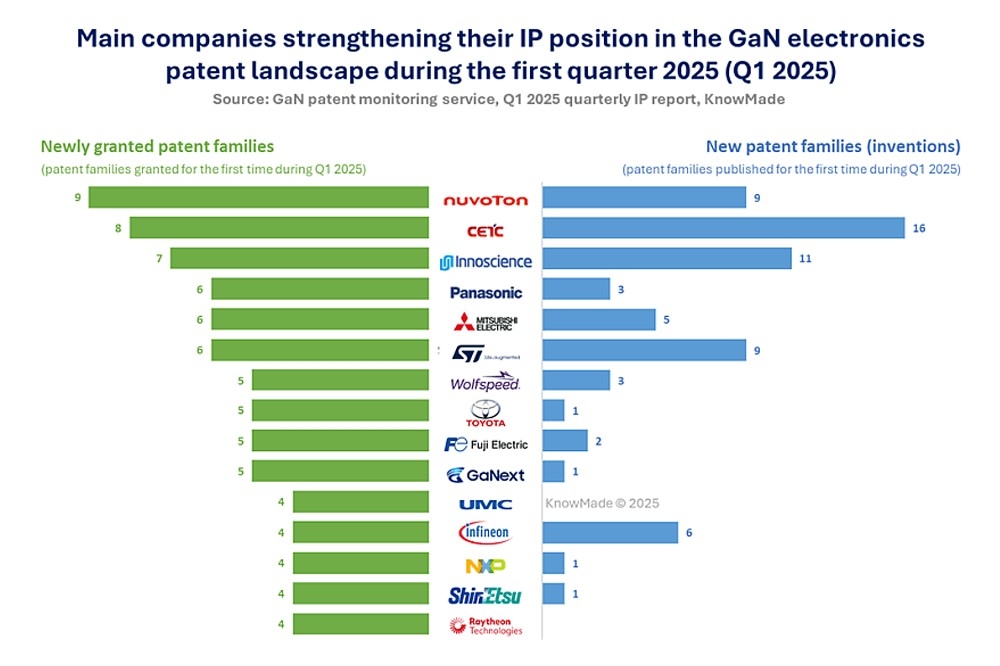

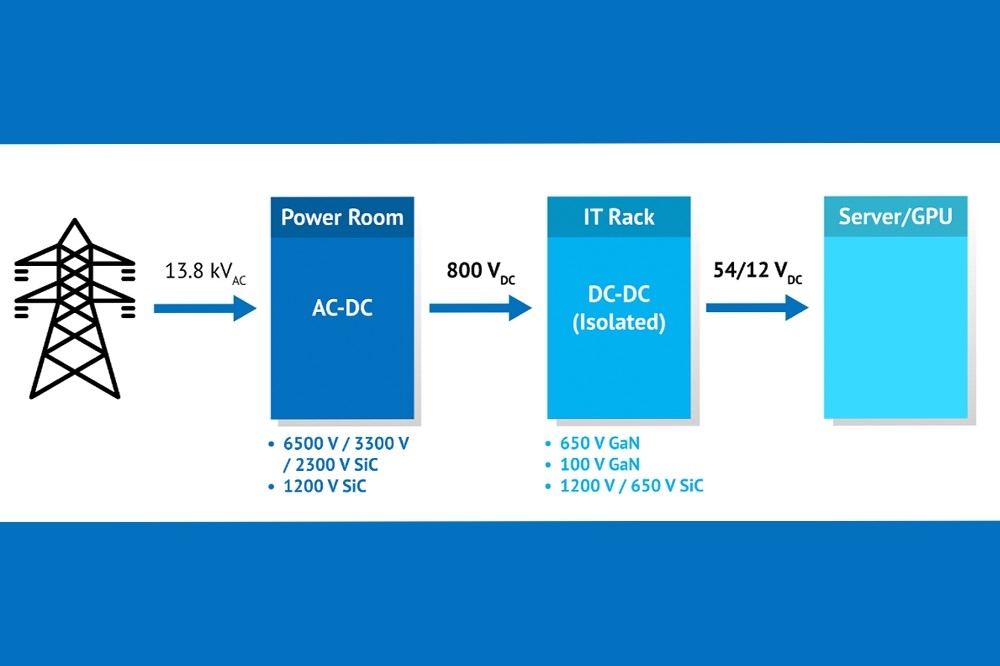

EDA company Silvaco has announced an R&D collaboration with Fraunhofer Institute for Silicon Technology (ISIT) to accelerate development of next-generation GaN devices.

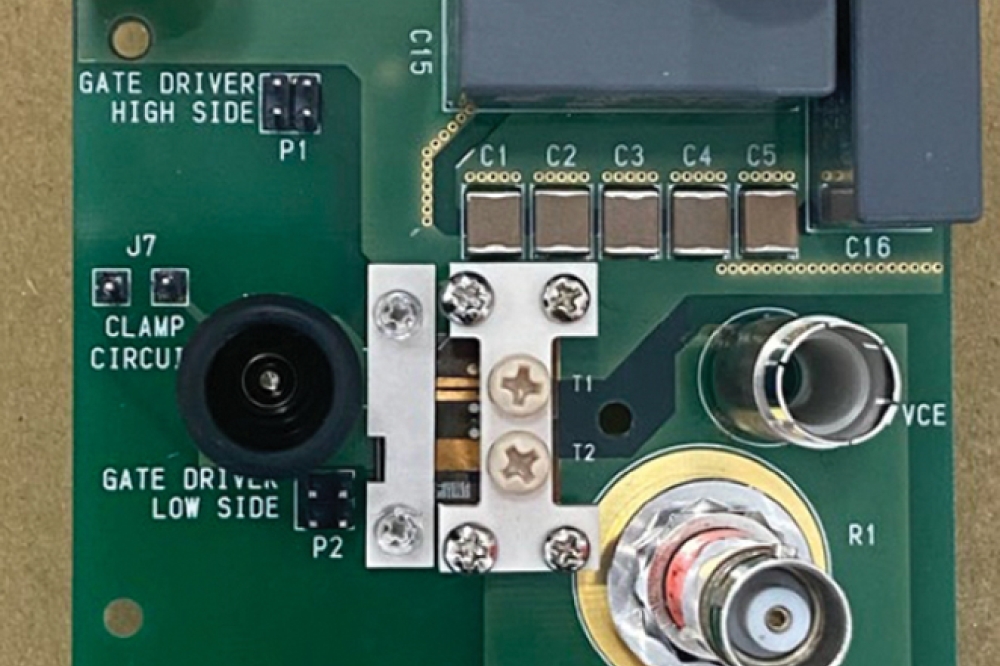

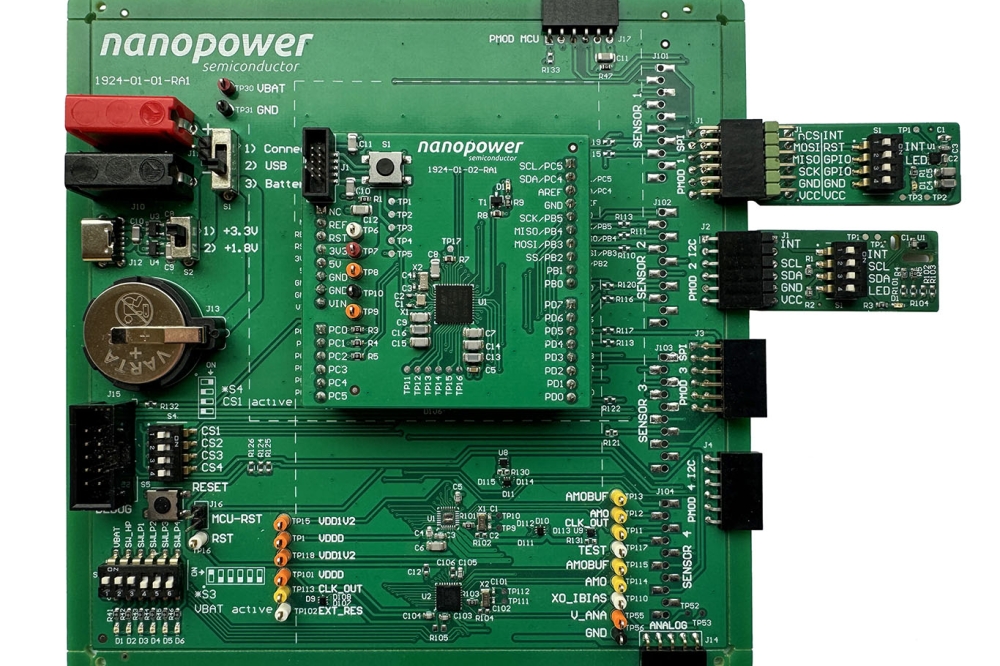

Fraunhofer ISIT’s Power Electronics division (which develops prototypes for power electronic and sensor systems) will use Silvaco’s design tools — including the Victory TCAD platform, Utmost IV, and SmartSpice — to perform Design Technology Co-Optimisation (DTCO) for device development.

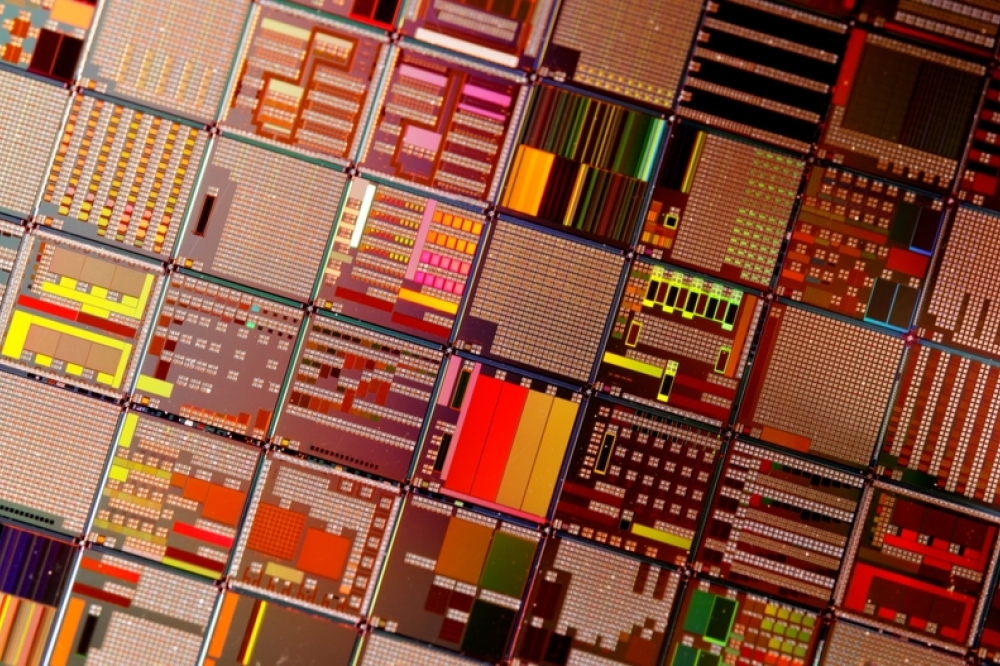

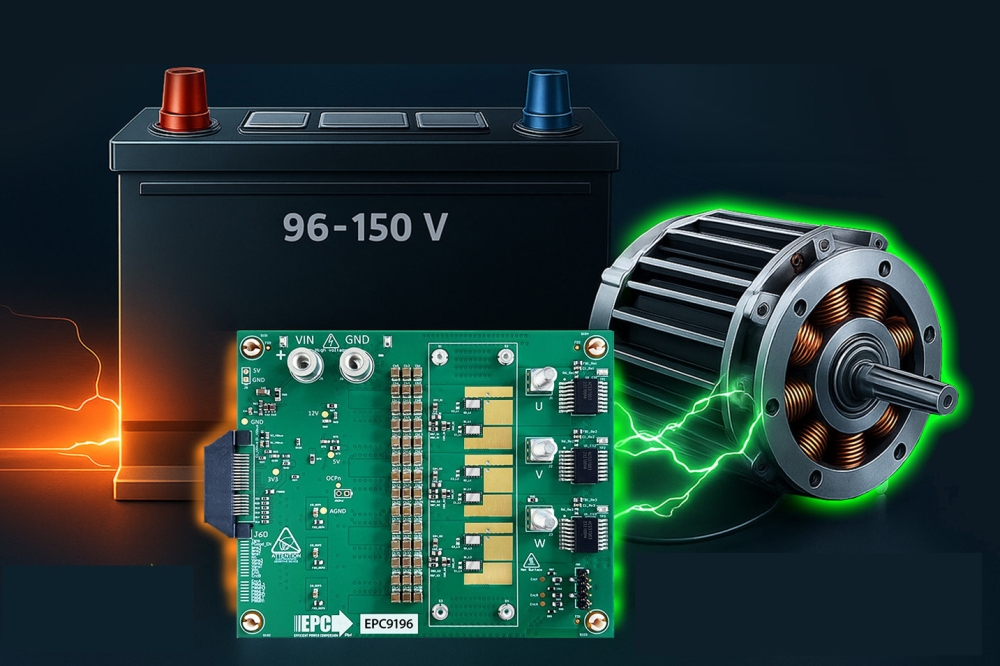

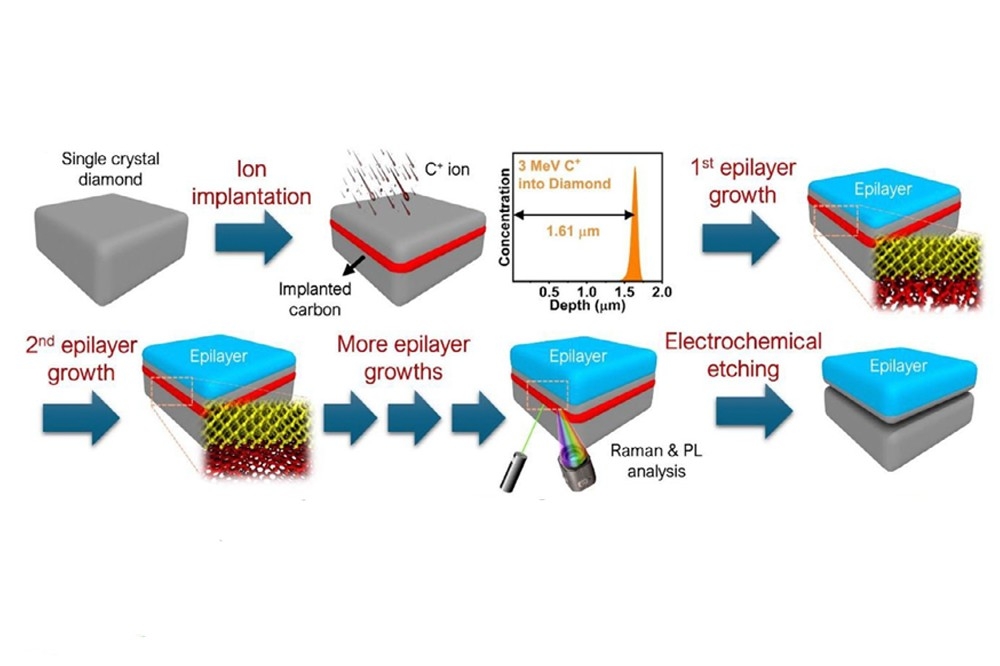

The idea is that Silvaco's DTCO platform will accelerate prototyping in Fraunhofer ISIT’s post-CMOS process environment, which is set up to explore emerging processes for both GaN and MEMS technologies on 8-inch wafers.

In addition, Silvaco’s Victory Design of Experiments (DOE) solution will streamline development workflows and support rapid innovation during the evaluation of novel process modules and emerging device concepts.

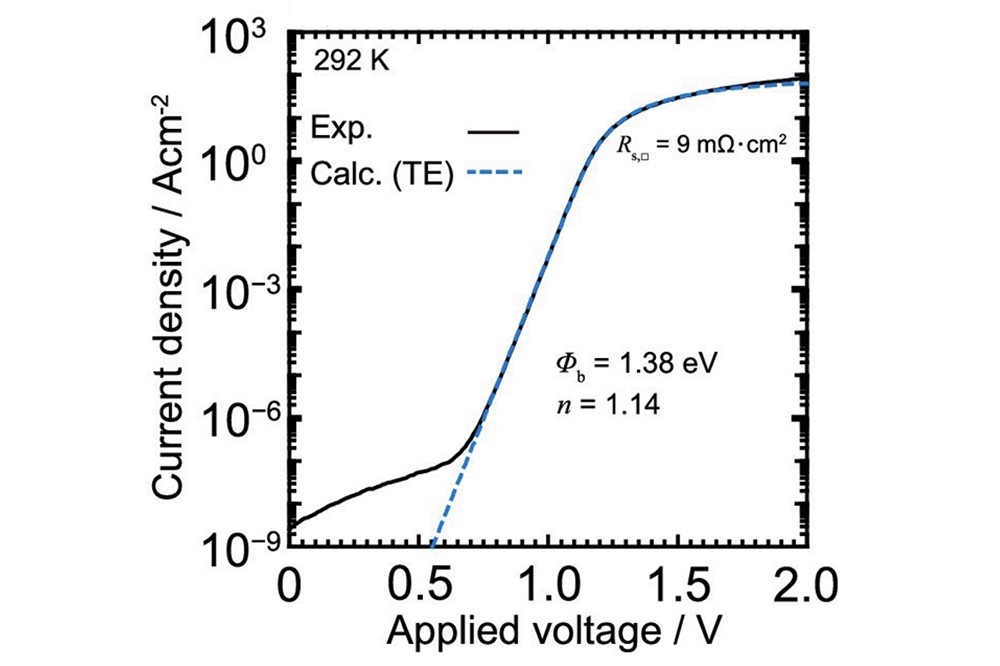

“We are excited to expand our GaN design capabilities with Silvaco’s Victory products,” said Michael Mensing, head of the Advanced Devices Group at Fraunhofer ISIT. “By using Silvaco’s advanced TCAD solutions, our teams can explore, understand, and optimise the performance of GaN devices with greater depth and efficiency. Especially during our current development of high voltage lateral and vertical GaN devices based on engineering substrates, like Qromis Substrate Technology, we see many physical effects that require accurately calibrated process and device models.”

“This collaboration marks a significant step forward in strengthening Europe’s semiconductor capabilities and driving the global evolution of GaN devices,” said Eric Guichard, SVP and general manager of Silvaco’s TCAD Division. “Institutes like Fraunhofer ISIT are instrumental in pushing the boundaries of innovation in device and process technology. By collaborating with Fraunhofer ISIT, we not only accelerate their development efforts but also enhance our own TCAD tools to meet the demands of future device design.”