Increasing power density, reducing power consumption

At the recent International Solid-State Circuits Conference (ISSCC) 2024, CEA-Leti and the University of California San Diego reported on the development of an IC for piezoelectric resonator DC-DC conversion achieving a 310% loss reduction. In a separate paper, CEA-Leti also described a novel architecture for keyword-spotting in always-on, voice-activated edge-AI systems – delivering accurate speech recognition at power consumption below one microwatt.

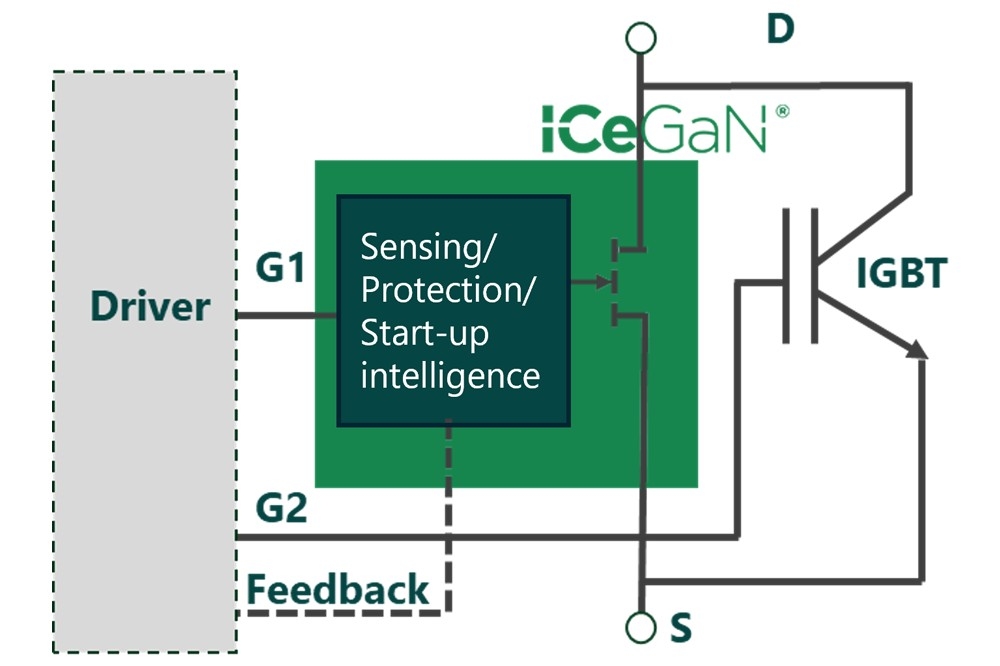

UNIVERSITY OF California San Diego and CEA-Leti scientists have developed a ground-breaking piezoelectric-based DC-DC converter that unifies all power switches onto a single chip to increase power density. This new power topology, which extends beyond existing topologies, blends the advantages of piezoelectric converters with capacitive-based DC-DC converters.

The power converters the team developed are much smaller than the huge, bulky inductors currently used for this role. The devices could eventually be used for any type of DC-DC conversation, in everything from smart phones, to computers, to server farms and AR/VR headsets. The results were presented in the paper, “An Integrated Dual-side Series/Parallel Piezoelectric Resonator-based 20-to-2.2V DC-DC Converter Achieving a 310%Loss Reduction”, Feb. 20 at ISSCC 2024 in San Francisco.

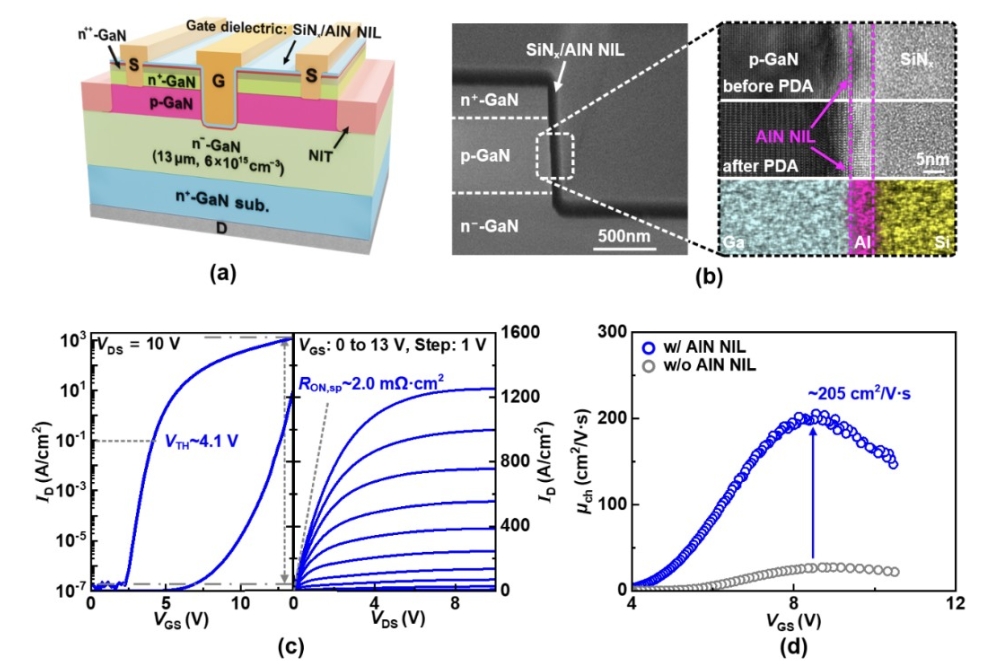

“The Dual-side Series/Parallel Piezoelectric Resonator (DSPPR) is the first IC used for PR-based power conversion, and achieves up to 310% loss reduction over prior-art published and co-designed discrete designs for VCRs<0.125,” the paper reports.

“This innovative approach enhances performance, especially at low voltage conversion ratios—an area where prior works struggled to sustain both high efficiency and optimal utilization of piezoelectric materials,” said Patrick Mercier, a professor in the Department of Electrical and Computer Engineering at UC San Diego and a senior author of the paper.

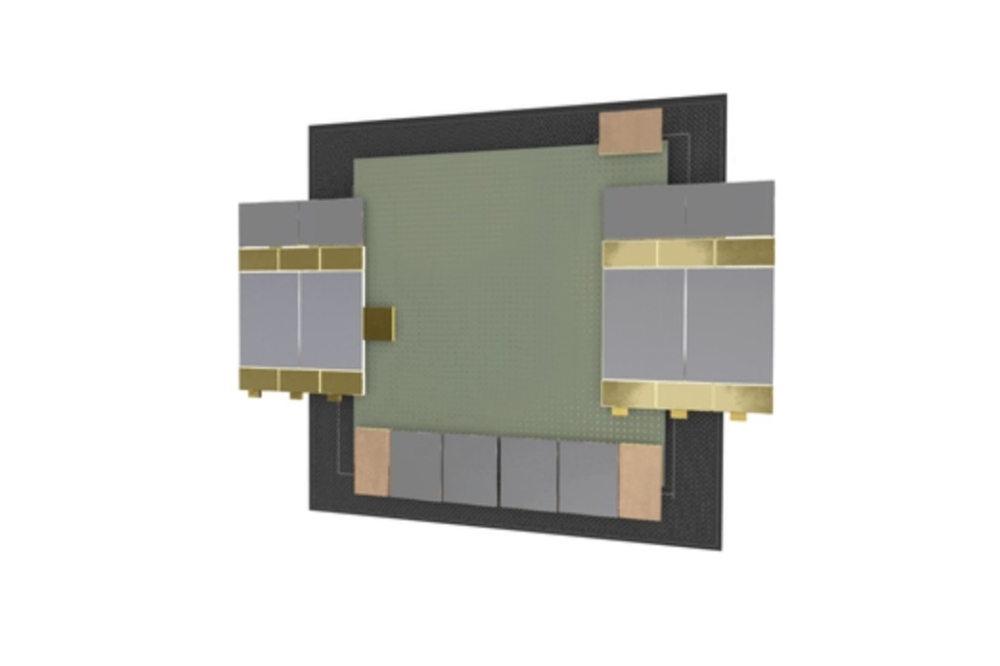

The paper explains that a hybrid DSPPR converter exploits integrated circuits’ ability to offer sophisticated power stages in a small area compared to discrete designs, and enables efficient device operation at voltage conversion ratios (VCR) of less than 0.1.

“The IC provides a distinct opportunity to consolidate all power switches onto a single chip, significantly diminishing the PCB footprint and enhancing phase-control precision,” said Gael Pillonnet, scientific director of CEA-Leti’s Silicon Component Division.

In addition, incorporating additional capacitive-based converter stages, both pre- and post- the piezoelectric DC-DC converter, contributes to performance improvement. “This strategic integration reduces the demand on piezoelectric material, resulting in a more compact converter with a notably smaller total volume. The marginal increase in additional capacitors, which is less than 10 percent, pales in comparison to the substantial gains facilitated by the proposed topology,” Pillonnet said.

“The DC-DC converter, particularly in the low VCR range, which was a focus of our work, has widespread applications in various sectors, such as high-power computing servers, automotive systems, USB chargers, and battery-powered devices,” said Wen-Chin Brian Liu, a Ph.D. student in Mercier’s research group and the lead author of the paper.

Accurate speech recognition, low power consumption

CEA-Leti has developed a keyword-spotting system that dramatically improves accuracy in always-on, voice-activated Edge-AI systems and that consumes less power in a far smaller silicon footprint than current technology.

Presented in a paper at ISSCC 2024 in San Francisco, the new architecture uses time-domain signal processing on oscillators locked by injection and is suitable for devices running on energy harvesters, which supply power below 0.5V. The paper, “0.4V 988nW Time-Domain Audio Feature Extraction for Keyword Spotting Using Injection-Locked Oscillators”, reports accurate speech recognition at power consumption below one microwatt. It describes the first injection-locked, oscillator-based time-domain audio feature extraction (TD-FEx) demonstrating keyword spotting operating down to 0.4V, while achieving 91 percent accuracy on 10 words. TD-FEx information is not coded as a voltage but as a time delay of two clocks’ signals. In addition to being well suited for advanced nodes, its advantages are digital-like implementation with low-supply voltage and better noise immunity than current systems. CEA-Leti’s system demonstrated accurate speech recognition with power consumption below 1 µW.

Some analog-based audio feature extraction (FEx) units using multi-channel Gm-C bandpass filters can supply 10 times the power efficiency of digital FEx units in a comparable silicon area. “However, analog FEx circuits have not demonstrated KWS with more than four keywords,” the paper reports. “They also suffer from a large footprint, challenging technology migration and limited dynamic range at low supply voltage, while speech signals have inherently a high dynamic range.”

“Our system’s silicon area of 0.15mm2 is at least 3.5 times smaller than prior art on the same process node of 65nm,” said Ali Mostafa, lead author of the paper. “With a power of 988nW, our system is nine times more power-and-area efficient than ring-oscillator-based TD-FEx.”

Applications beyond speech recognition for this system include predictive maintenance and health monitoring that require on-line frequency decomposition of the sensor data.