Saras joins two CHIPS packaging projects

Arizona-based Saras Micro Devices, a start-up focused on improving power performance using novel packaging, has announced its participation in two projects funded by the US Department of Commerce CHIPS National Advanced Packaging Manufacturing Program (NAPMP).

Each project was awarded $100 million in government funding.

One initiative is the Substrate-based Heterogeneous Integration Enabling Leadership Demonstration for the USA (SHIELD USA) project, led by Arizona State University (ASU) and Deca Technologies. The second is the Substrate and Materials Advanced Research and Technology (SMART) Packaging Program, led by Absolics.

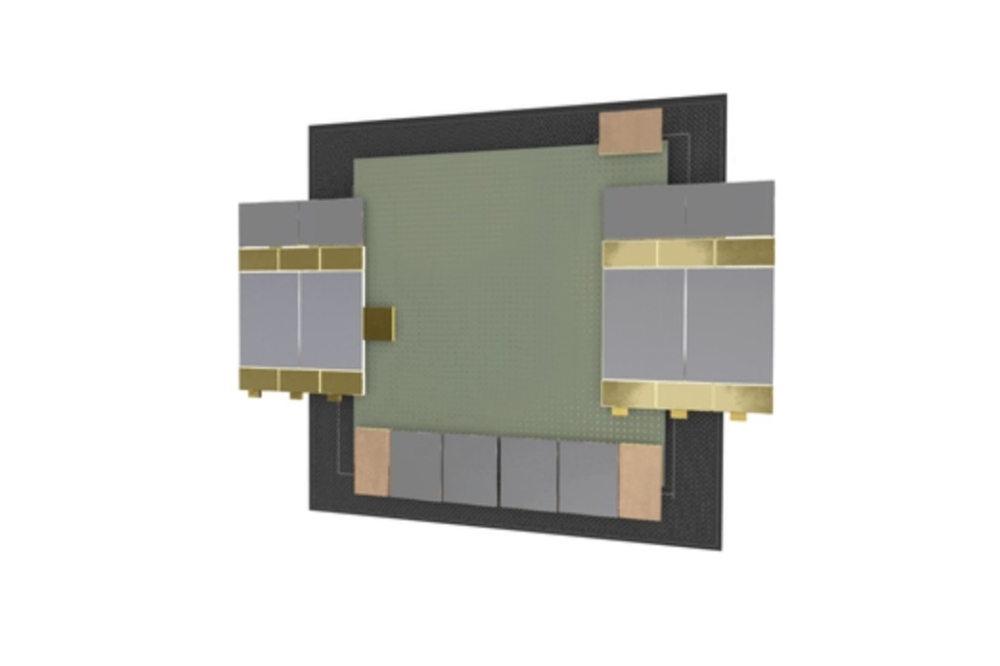

Saras will contribute the Saras Tile, or STILE, to both projects. This technology is a substrate-embedded, passive module, that moves power regulation from the board to package, reducing the number of separate components needed. It is designed to support the growing number of power rails within packages, with a focus on power delivery for next-generation AI and HPC devices.

“The power delivery challenges posed by AI require innovative solutions,” said Ron Huemoeller, CEO of Saras. “Our STILE technology addresses these challenges by enabling in-package power delivery close to the source, improving both efficiency and performance while opening up package real estate for higher levels of chiplet integration. By collaborating on the SHIELD USA and SMART projects, we’re able to contribute critical AI power delivery elements and, consequently, significantly advance US semiconductor manufacturing capabilities.”

Over the past year, Saras has secured seven patents for its capacitor and STILE technologies from the United States Patent Trademark Office.