A superior process for the SiC superjunction

Rounds of ultra-high-energy implantation and epitaxial growth enable the

realisation of devices with a SiC superjunction that block several

kilovolts.

BY REZA GHANDI FROM GE RESEARCH

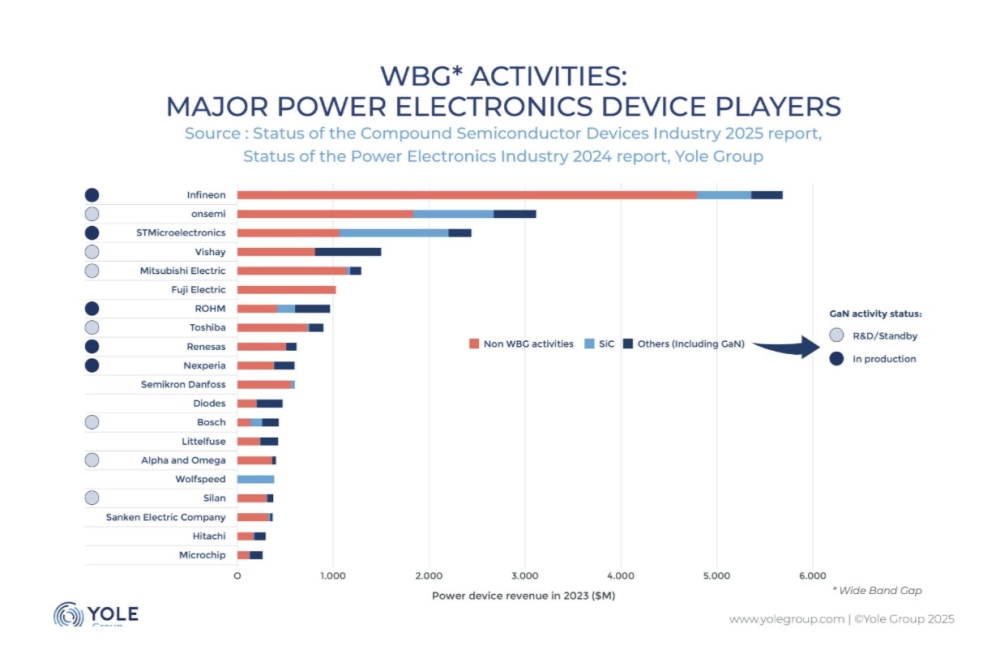

To trim the global carbon footprint much effort must be devoted at improving electrical infrastructure. As well as the most obvious priority on that front – increasing the proportion of energy that’s generated from renewable sources – there needs to be an increase in the efficiency of electrical transmission, right from where power is generated to where it is used.

A key part of electrical infrastructure is the medium-voltage power-conversion system, which may be used in wind turbines, solar installations and marine converters. Operating at voltages above 3.3 kV, this class of power-conversion system is limited to switching frequencies of no more than several hundred hertz, due to losses in silicon-based solid-state switches and diodes. That’s far from ideal, because at these low frequencies transformer and converter filter weights can be as high as several tons, which increases system and installation costs and limits design flexibility. What’s needed is a shift to highly efficient, lightweight, multi-megawatt/multi-kilohertz power-conversion systems based on ultra-high-voltage power semiconductor devices that switch at moderate frequencies, such as 1-20 kHz.

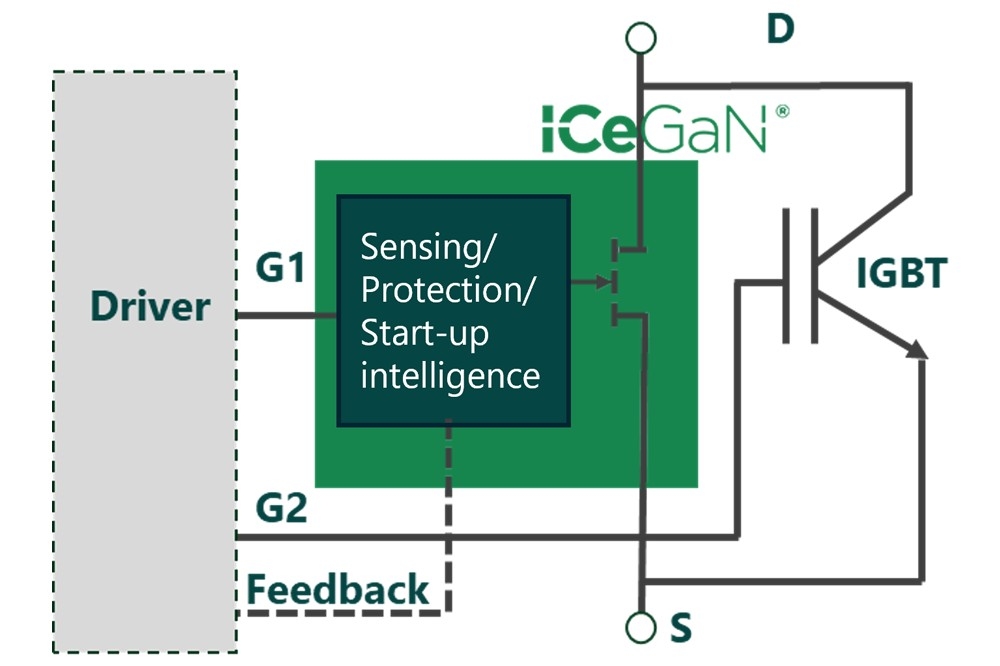

Figure 1. Schematic view (left) and scanning electron microscopy,

cross-sectional view (right) of GE’s 4.5kV SiC charge-balanced (CB)

MOSFET. These switches implement epitaxial regrowth and high-energy

implantation similar to SJ devices.

If you are a regular reader of this publication, you will know that SiC devices can solve many of the limitations of the silicon-based incumbents. But at blocking voltages of several kilovolts, success with this approach is far from trivial. A formidable challenge arises because at blocking voltages of 3.3 kV or more, SiC unipolar switches and diodes suffer from high conduction losses at elevated temperatures, while SiC bipolar devices, such as IGBTs, exhibit a prohibitive high forward-voltage drop of 3 V. Therefore, in these systems, the advantages of SiC technology over that of the silicon IGBT are diminished.

One solution that’s attracted interest is the SiC superjunction. This architecture breaks the unipolar conduction limit and offers an improved trade-off between the specific on-resistance and the blocking voltage in medium-voltage-class applications.

To date, there have been a few demonstrations of this device. They include multi-epitaxial SiC superjunction devices that span 1.2- 3.3 kV, and are formed with a multi-epitaxial approach. Fabricating such devices is not straightforward, as it requires several iterations of epi regrowth, due to the shallow projectile depth of implanted atoms in SiC using conventional process tools. An alternative is to make a trench-refill SiC superjunction device. However, although that device can handle 6.5 kV, it suffers from excessive leakage at high blocking voltages, due to crystallographic defects from a complex refill process.

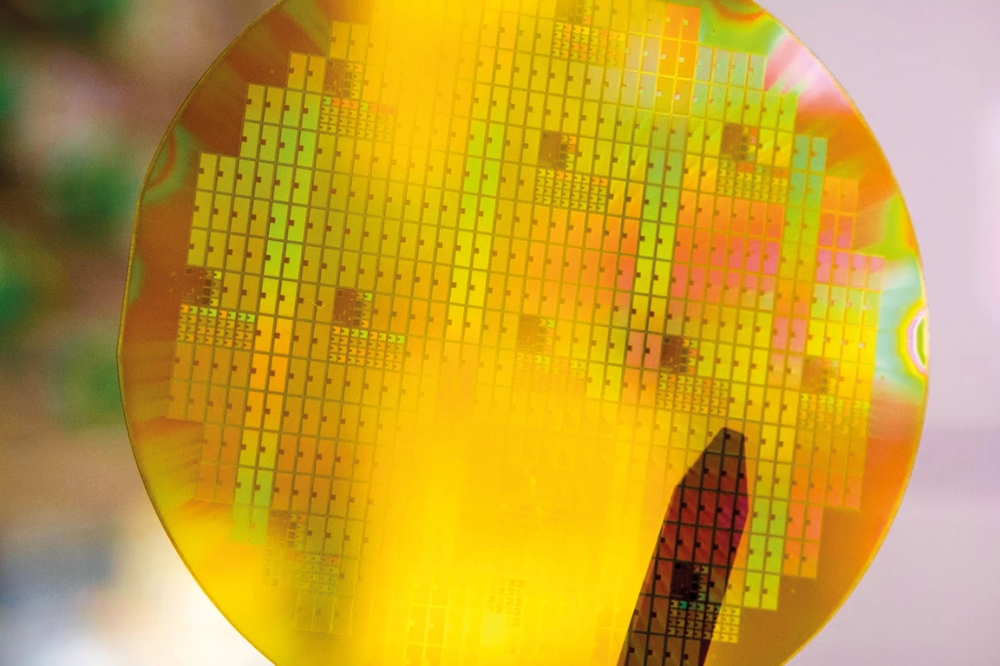

Figure 2. World’s first 3.5 kV deep-implanted SiC superjunction,

junction barrier Schottky (JBS) diode with two rounds of epitaxial

overgrowth and ultra-high-energy implantations fabricated at GE

Research.

At GE Research we are currently exploring a novel, third fabrication architecture for producing devices operating above 3.3 kV, based on ultra-high-energy implantation and epitaxial growth. This technology draws on our pioneering capabilities in SiC charge-balanced device fabrication, developed from a recently completed project funded by ARPA-E (the ARPA-E DE- AR0000674 “SiC charge balanced FETs for Breakthrough Power Conversion” programme). In that programme, we developed a superjunction intermediate charge-balanced technology. This involved the implementation of a novel drift layer architecture, to create buried charge-balanced p-type regions, which are electrically connected to the top body contact through mega-electron-volt, high-energy implanted regions (denoted P-Bus, as shown in Figure 1). As is the case with superjunction pillars, if the charge-balanced regions are designed with the optimum implanted p-type dose and spacing, they deplete surrounding areas during blocking and act as electric field dividers. The key implication is that for a given breakdown voltage, it is possible to use a drift layer with higher doping than that in a traditional design, that enables a lower on-resistance in forward conduction mode and obliterates the conventional, one-dimensional limits for the specific on-resistance as a function of breakdown voltage.

Using this approach, we began by producing devices that have a comparable performance to that of a 20 µm pitch SiC superjunction – and are significantly better than state-of-the art high-voltage SiC approaches. Recent highlights from that effort include the first experimental demonstration of charge-balanced MOSFETs with a differential specific on-resistance of 10 mΩ cm2 and a blocking voltage of more than 4.5 kV. This value for the specific on-resistance is below the one-dimensional specific on-resistance as a function of blocking voltage, and is nearly 20 percent below that for conventional 4.5 kV SiC FETs reported. To our knowledge, this is the highest breakdown voltage for any SiC charge-balanced device demonstrated to date, and the lowest on-state loss for any 4.5 kV-class MOSFET reported.

While we are encouraged by this success, we know it’s just a start. One downside of this device is that due to its stacked nature for charge balancing, and the charge carrier redistribution required during switching, there are switching delays, which increase with each additional layer. These delays are prohibitive when scaling SiC charge-balancing devices beyond 4.5 kV.

To build on our initial efforts, we are now extending our charge-balance architecture to full superjunction devices, supported by further funding from ARPA (ARPA-E DE-AR0001007 “Advanced Medium Voltage SiC-SJ FETs with Ultra-Low On-resistance”). Our latest work involves the fabrication of full superjunction devices based on deep implanted pillars, developed for charge-balance devices to overcome the limitations imposed by the charge-balance carrier distribution delay.

Breaking new ground, our team has demonstrated the world’s first 3.5 kV SiC superjunction deep-implanted junction barrier Schottky (JBS) diodes (see Figure 2). These devices, a significant milestone for SiC, will provide a stepping stone for our development of 3.3 kV SiC SJ MOSFETs.

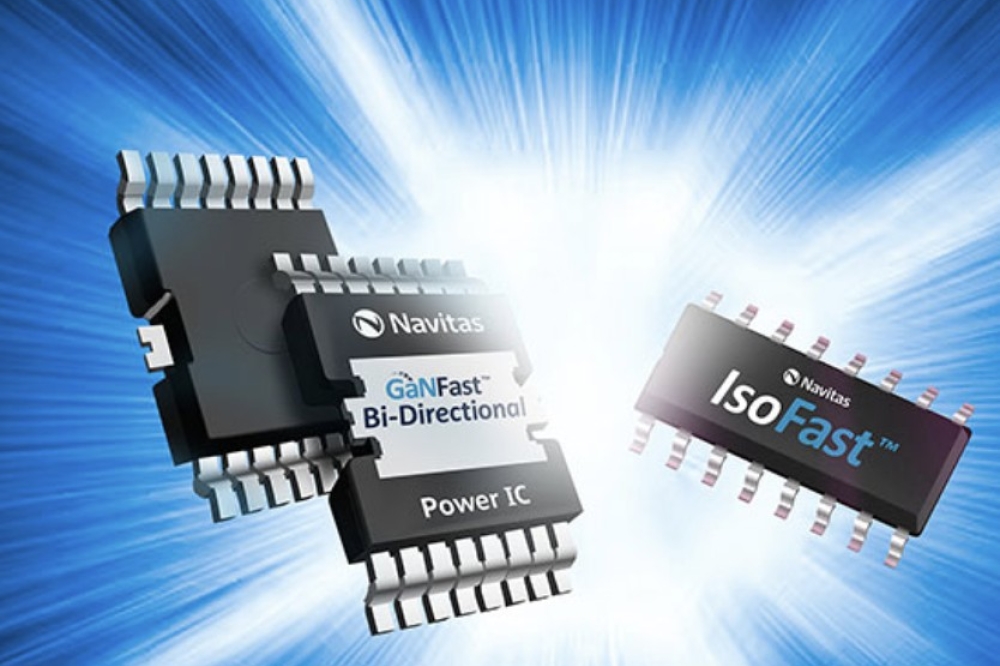

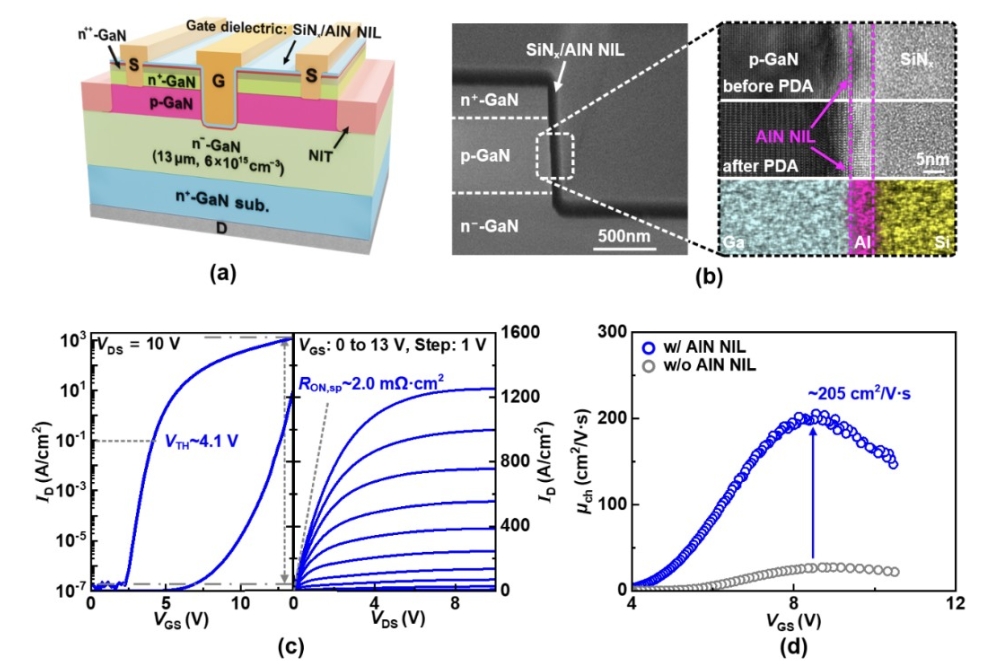

Figure 3. Forward and reverse current-voltage (I-V) characteristics of

3.5 kV deep-implanted SiC superjunction, junction barrier Schottky (SJ

JBS) diode. The specific on-resistance, Ron,sp is 4.5 mW cm2 (45 percent

below SiC unipolar limit).

The deep-implanted superjunction diodes that we have produced are formed using two rounds of epitaxial overgrowth (12 µm each), leading to a total drift layer thickness of 24 µm. The p-doped and n-doped pillars were created using two rounds of high-energy implantations (MeV), enabling a maximum junction depth of 12 µm.

We have measured the forward and reverse current-voltage characteristics of our superjunction JBS diode (see Figure 3). This device turns on at 1.4 V and has a specific on-resistance of 4.5 mΩ cm2 at room temperature and 9.6 mΩ cm2 at 150 °C, which is about 45 percent below the SiC unipolar limit. Breakdown voltage is 3.8 kV. We have observed low leakage prior to breakdown, suggesting that there is low defectivity following high-energy implantation, epitaxial overgrowth and an activation anneal at 2,000 °C.

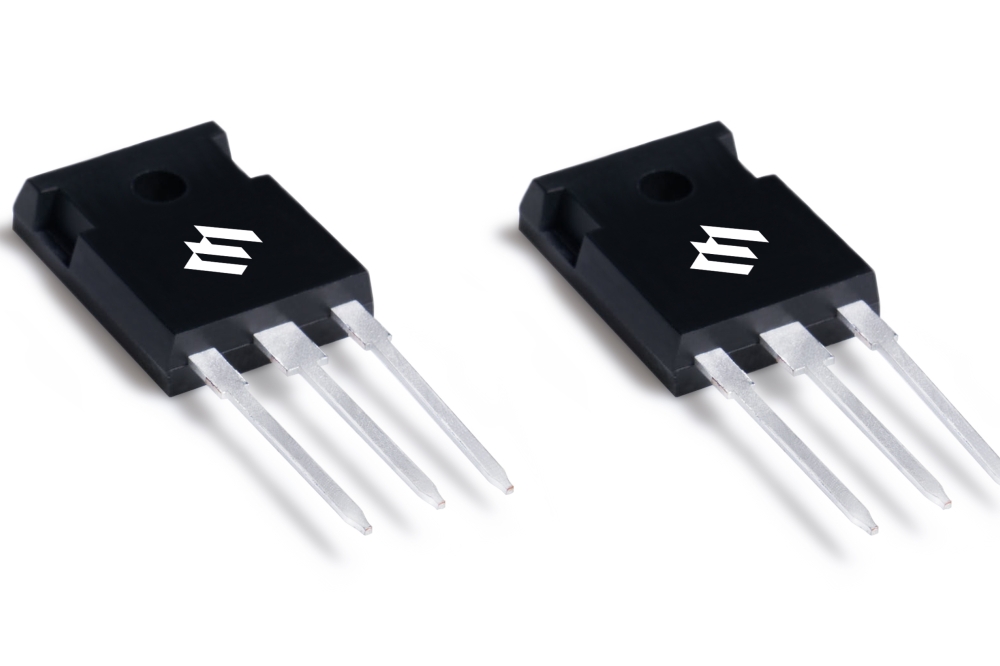

Figure 4. Reverse recovery characteristics of 3.5 kV SiC deep-implanted

superjunction, junction barrier Schottky (SJ JBS) diodes at room

temperature and 150°C.

Using the ITC57300/57220 from AGVA Technologies (see Figure 4), we have carried out reverse recovery measurements of SiC superjunction diodes. We did not observe any change in the turn-off current and voltage waveform when increasing the junction temperature from ambient to 150 °C. We estimate the total capacitive charge to be below 700 nC/cm2.

Figure 5. Comparison between GE’s reported charge-balanced and

deep-implanted superjunction devices, together with the 4H-SiC unipolar

and superjunction limits.

Benchmarking our charge-balanced and superjunction devices against 4H-SiC unipolar devices and superjunction limits demonstrates the effectiveness of both our technologies (see Figure 5). They are an attractive alternative to the multi-epitaxial and trench-refill approaches to making superjunction devices, and they offer a scalable solution towards the realisation of medium-voltage-class, high-frequency, solid-state switches.

•The information, data, or work presented herein was funded in part by the Advanced Research Projects Agency-Energy (ARPA-E), U.S. Department of Energy, under Award Number DEAR0000674 and DEAR0001007 advised by Program Director Isik Kizilyalli. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

Further reading

“IGBT and Diode chips from ABB Switzerland Ltd, semiconductors.” Available at www.abb.com

A. Bolotnikov et al. 2015 IEEE Appl. Power Electron. Conf. Expo., pp. 2445–2452.

L. Han et al. “A Review of SiC IGBT: Models, Fabrications, Characteristics, and Applications” IEEE Trans. Power Electron. 36 2080 (2021)

T. Tanaka et al “First Demonstration of Dynamic Characteristics for SiC Superjunction MOSFET Realized using Multi-epitaxial Growth Method,” 2018 IEEE Int. Electron Devices Meet., p. 8.2.1-8.2.4, 2019.

M. Baba et al. “Ultra-Low Specific on-Resistance Achieved in 3.3 kV-Class SiC Superjunction MOSFET,” 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2021, pp. 83-86

R. Kosugi et al “Breaking the Theoretical Limit of 6.5 kV-Class 4H-SiC Super-Junction (SJ) MOSFETs by Trench-Filling Epitaxial Growth,” in 2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2019, pp. 39-42.

P. Thieberger et al. “Novel high-energy ion implantation facility using a 15 MV Tandem Van de Graaff accelerator,” Nucl. Instruments Methods Phys. Res. Sect. B Beam Interact. with Mater. Atoms 442 36 (2019)

R. Ghandi et al. 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Sep. 2020, pp. 126–129.

Z. Chen et al. “Effect of Annealing Conditions on Recovery of Lattice Damage in a High-Energy-Implanted 4HSiC Superjunction PIN Diode,” ECS Journal of Solid State Science and Technology 11 065003 (2022)