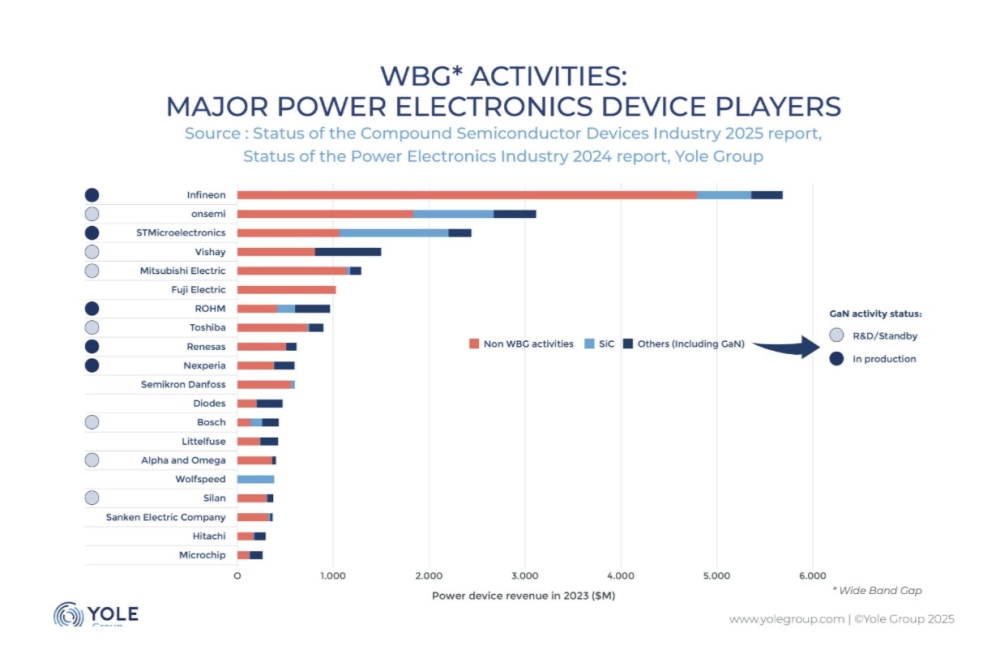

International Reliability Physics Symposium: Superior testing of SiC

Speakers at the International Reliability Physics Symposium detail the

most insightful approaches for evaluating the long-term capability of

SiC power devices.

BY RICHARD STEVENSON, EDITOR, CS MAGAZINE.

At the very earliest stages of development of any power device, the focus is always on instantaneous performance characteristics, such as on-resistance, blocking voltage and peak current delivery. But it’s not that long until evaluation expands to include insights into reliability. After all, if the device doesn’t last long enough to serve in any practical application, it will never be commercially viable.

As the device matures and volume production begins, new questions need answering when assessing reliability. For example, there is a need to know what fraction of devices will fail at any point in time. It’s also beneficial, from the perspective of the customer base, to vary the conditions of assessment to reflect different applications; and it may be crucial to pinpoint any drifts in key characteristics, even if this doesn’t lead to device failure, as it could still be a compromise too far.

All these sorts of questions are now being asked of SiC transistors and diodes, power devices that are well beyond the stage of simply being promising – they are netting billions of dollars per year, with sales ramping fast.

Insights into better approaches for assessing the reliability of SiC power devices, alongside commentary considering what traditional methods may overlook, formed the heart of several presentations at the recent International Physics Reliability Symposium.

At this meeting on 28 to 30 March, held on-line and also in person in Monterey, CA, illuminating talks on SiC included those from: ABB’s Elena Mengotti, who revealed the various tests that this company is using to assess the reliability of SiC MOSFETs from different suppliers; Kin Cheung from NIST, who explained why exceptional wafer cleaning fails to guarantee a great gate oxide; and Peter Moens from onsemi, who made a strong case for distinguishing between the lifetime of the SiC MOSFET and its useful time.

Figure 1. ABB evaluates SiC power devices with a variety of tests. Two

half-bridge legs subject devices to stress, with characterisation

following this procedure.

Seeking standardisation

Mengotti, a Principal Scientist at ABB’s Corporate Research Centre in Switzerland, claimed that one of the issues surrounding SiC power devices is the variation in testing.

“The standardisation of silicon carbide diodes and MOSFETs has not yet converged to a set of stable and specific tests to pass that the industry can simply request from the supplier,” argued Mengotti.

While she is in no doubt that SiC outperforms silicon, she points out that any new technology introduces new failure mechanisms. Consequently, new qualification methodologies are needed to minimise the risk during initial device deployment.

Taking action on this front, ABB has developed a number of in-house tests, covering both the chip and the package.

One such test is that of avalanche ruggedness, an assessment that’s suitable for applications where there is a switching of the inductive load. At ABB this test, conducted on chips in a TO-247 package, begins by charging the load inductor with a current that’s low enough to avoid device self-heating.

Figure 2. The H3TRB-HVDC test carried out at ABB runs for 1200 hours and

involves a temperature of 85 °C, a relative humidity of 85 percent, and

a drain-source voltage of 80 percent of the maximum value. The leakage

current recorded throughout this test reveals substantial differences

between suppliers.

The device is then turned off, with avalanche

energy dissipated in the MOSFET. Those carrying out this test determine the destruction energy limit for five samples, before conducting further tests on eight MOSFETs, using 100 pulses with an energy that’s 95 percent of that of the destruction limit.

ABB uses its avalanche ruggedness test to assess SiC MOSFETs from six different suppliers. “Pre- and post-stress curves did not show sign of ageing electrically,” remarked Mengotti. “The avalanche ruggedness of state-of-the-art silicon carbide MOSFETs is sufficient to allow unclamped switching of inductive loads.”

Another test at ABB, helpful for determining how SiC power devices behave during start-up and shut-down procedures in grid-connected solar and wind farms, is a study of the repetitive surge current.

“During the test we stress the silicon carbide diode or the body diode of the MOSFET, which is supposed to be a weak part of the device,” said Mengotti.

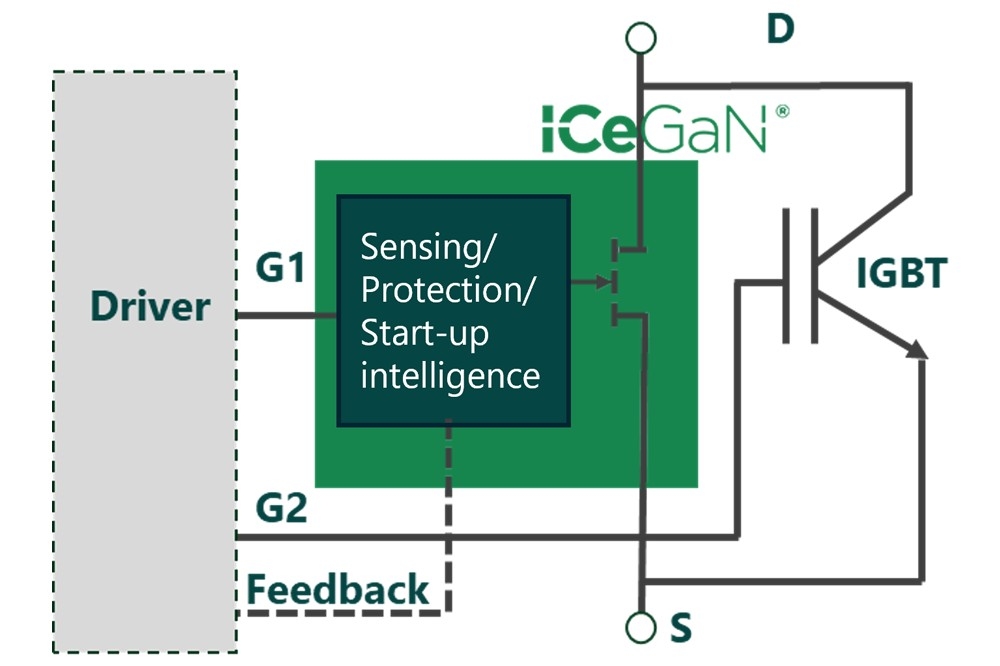

The set-up involves two half-bridge ‘legs’ (see Figure 1). One generates rectangular high-current pulses with a 10 ms width at a frequency of 10 Hz. The other leg delivers a blocking voltage that’s 80 percent of the nominal value between the surge pulses.

Using this approach, engineers at ABB evaluate devices by first increasing the surge current pulses, an approach that tests five samples to destruction. Then ten samples are aged with 1,000 pulses, using a current that’s 90 percent of the value that led to device destruction. After that characterisation of the devices is undertaken. “No electrical aging sign has been observed,” revealed Mengotti, who added that all of the SiC devices that have been tested show a very good level of reliability, in terms of repetitive surge current operation.

Also included in the testing suite at ABB is passive ‘dV/dt’ switching – this is also known as the dynamic reverse-bias test. For this evaluation, 20 devices are tested in parallel for 1000 hours, using a frequency of 60 kHz, and a dV/dt of 100 V/ns.

Using this test to monitor the drain source leakage indicated no sign of device aging. Only the very first generations of diodes showed an abrupt failure, due to an issue associated with edge termination.

“Since no failures were observed in devices from generation two onwards, and no ageing signs were seen, we currently regard this test as unnecessary,” remarked Mengotti.

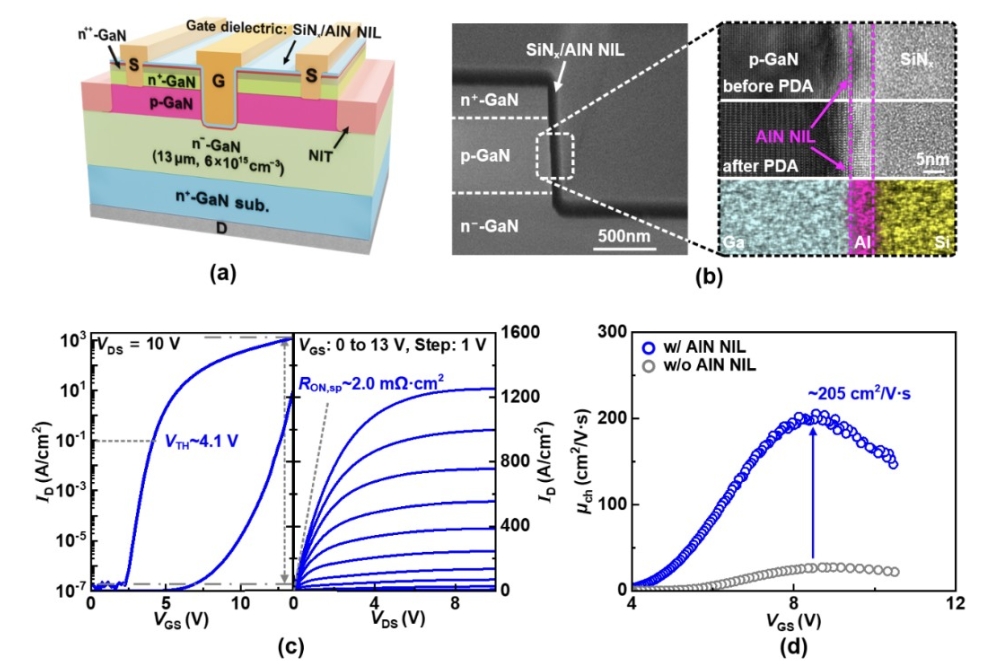

Figure 3. Simulations by NIST catering for variations to the energy of

the defect, the width of the energy distribution, and the density of the

defect, can model the extrinsic tail of failures associated with the

lucky defect.

There have always been concerns associated with the quality of the gate oxide in SiC MOSFETs. There are imperfections at the interface of SiO2 and SiC, and the dielectric oxide is relatively thin. To evaluate the quality of this oxide, the team at ABB elevates the temperature of the SiC MOSFETs to 175 °C, steps up the voltage every 24 hours and monitors the threshold voltage and the gate leakage current.

Using this approach, Mengotti and co-workers have aged 30 planar and 30 trench MOSFETs simultaneously. “The trench [devices] failed at a latter voltage value, indicating higher robustness than the planar. But the planar presented a lower standard deviation, indicating a more mature technology,” revealed Mengotti. Another plus for the planar device over its trench cousin is a lower failure rate at the use condition, in terms of gate voltage.

The representative from ABB also discussed a number of other reliability tests for chips. They involved subjecting them to: a high reverse bias, which indicated that reliability is beyond expectation; transfer curves, to study threshold voltage hysteresis; transient measurements of drain current, which revealed that SiC MOSFETs behave differently to their silicon counterparts, but there is no cause for concern; and a test combining voltage and humidity, known as H3TRB-HVDC (see Figure 2 for details).

As well as all these chip-level tests, ABB carries out others at the package level, including power cycling, a test widely used for silicon MOSFETs. This examination involves looking at temperature differences after devices had undergone current cycling that increased their temperature to 80 °C. This test uncovered a difference between packaged devices that had wires soldered and sintered to the baseplate of a SiC MOSFET. “The failure for the solder is reached at around 50,000 cycles, with a smooth increase in the ‘delta-T’ junction that is proven to be a solder die attach failure mechanism, while for the same temperature condition, the number of cycles has improved to around 90,000 for the sintered junction,” remarked Mengotti. In the latter case, failure is due to a wire bond lift-off.

Figure 4. Investigations by onsemi reveal that gate currents of a SiC

MOSFET show a similar trend, for a range of voltages and stress times.

The gate current is initially flat, before it drops and then rapidly

climbs, due to failure. A ‘use’ time, referred to as t0, can be defined

from the intercept of two lines: one for the gradient of the flat part

of the curve, and a second from when it is dropping.

The lucky defect model

A presentation by Kin Cheung, a Project Leader at NIST, provided a more detailed discussion relating to concerns associated with the gate oxide of SiC MOSFETs.

“A few years ago, I heard from a number of silicon carbide companies that there is a persistent, extrinsic tail in the breakdown distribution,” remarked Cheung, who explained that this small proportion of problematic devices remained after exhaustive efforts to clean the wafer.

He said that at this time, this was considered a specific SiC problem, because a thermal oxide grown on SiC has more defects than a thermal oxide grown on silicon. When SiC is oxidised, as well as the addition of SiO2, CO2 is also added – it cannot easily escape the oxide layer, and may lead to trapped carbon.

One may expect that this extrinsic breakdown problem is unique to SiC. But that’s not the case. Cheung pointed out that it has also been reported in silicon, back in 2007, for an oxide thickness of 55 nm.

Historically, there has been just one model for extrinsic failure, based on local thinning. It’s been argued that local thinning, caused by particulates and contamination, leads to a lower growth rate that is to blame for a higher electric field in that region and ultimately an earlier device breakdown. But if that were the cause, there’s no explanation for extrinsic failure in cleaned wafers.

A model that can do just this is the ‘lucky’ defect model, which Cheung championed. He argued that while debate continues over the cause of breakdown in the oxide of SiC devices, there is consensus that this failure mechanism is related to current flow across the dielectric, with higher currents leading to a shorter lifetime.

As well as local thinning, trap-assisted tunnelling can increase the current, remarked Cheung: “If you have defects at the right energy and the right spatial location, this can greatly enhance the tunnelling probability through the trap-assisted tunnelling mechanism.” When this happens, there’s an increase in the local current, leading to a shortening of device lifetime.

Cheung said that there is a sweet spot at which the effect is strongest. “The effect decays away rapidly as you move away from the sweet spot. That is the reason why it’s called a lucky defect model.”

It’s important to note that with the lucky defect model, even if the oxide is grown on a perfectly clean wafer, defects will still be present. Simulations confirmed this, modelling a 50 nm-thick oxide with a defect density of 1 x 108 cm-3 (see Figure 3). To produce this plot, Cheung and co-workers considered variations to the defect’s energy, its density, and the width of its energy distribution.

“The good news is that the lucky defect model gives you another way to further improve the extrinsic failure distribution, which is to improve the growth process,” remarked Cheung. “Some companies have reported that improving the growth process did help to reduce the extrinsic failure, although exactly what they’ve done is proprietary information.”

The lucky defects have implications for common tests that are applied to SiC MOSFETs, such as those involving the ramping of voltage (V-ramp) and high-field screening.

Cheung explained that producing SiC MOSFETs that are completely free of extrinsic failures is both hard to realise and difficult to prove. When efforts are directed at improving the growth process, a technique is needed to determine whether changes are beneficial. The standard method for assessing the gate oxide – the time-dependent dielectric breakdown method – is far from ideal for this particular task. One major drawback is that this technique requires the measurements of many thousands of devices, because only a small proportion exhibit concerning characteristics.

“Some vendors prefer a much faster alternative, which is the V-ramp test. With that you improve your growth process,” explained Cheung. However, he added that to ensure product reliability in the field, it is very common for chipmakers to also use high-field screening before they ship their products.

But do these strategies actually work? “If extrinsic breakdown is due to local thinning, it likely does – at least, there is no strong evidence to say it wouldn’t work,” said Cheung. However, if extrinsic breakdown is due to lucky defects, it doesn’t.”

Determining the safe operating areaPeter Moens from onsemi also discussed concerns related to the gate dielectric in SiC MOSFETs. He pointed out that during gate stress, substantial charge trapping occurs in the dielectric. “This results in parametric shifts, limiting the use time of the device.” These shifts could cause device characteristics to stray outside the values given in the accompanying data sheets. To avoid that from happening, Moens championed the introduction of a ‘use time’, which he agued is preferential to a ‘lifetime’.

To promote this concept, Moens presented an internal study, considering 1.2 kV n-type SiC MOSFETs with a 30 A on current, an on-resistance of 20 mΩ and an oxide thickness of around 40 nm. Measurements were made at both the wafer level, and on chips housed in a TO-247 package.

“Typically, when people look at lifetime, they look at time to fail,” remarked Moens. “But it’s more instructive to look at the complete gate current versus time characteristics.”

Plots of this for a device temperature of 175 °C show that initially the gate current is almost flat, before it drops significantly due to electron trapping, and then hikes when the device fails (see Figure 4). This trend is seen for different gate voltages and for stress times of up to 7 months, with plots revealing what Moens refers to as an “envelope curve” that is independent of both gate voltage and temperature. “And strangely enough, this same envelope curve is also observed on silicon technologies,” added Moens, who said that this finding shows that device behaviour must be related to the characteristics of SiO2.

Based on the plots, Meons suggested that rather than giving a lifetime for SiC MOSFETs, it is more insightful to give a use time, defining this as the intercept of the flat gate-current curve with that of the envelope curve. The use lifetime, given the moniker t0, can also define the safe operating area – this corresponds to a timeframe when the on-resistance shifts by only around 10 percent and the shift in threshold voltage is below 1.2 V. In comparison, between t0 and device failure, the on-resistance can change by more than 100 percent.

Meons and co-workers have also considered SiC MOSFET behaviour at 0 °C, a temperature where hole trapping occurs. Due to this, during gate stress an there’s initial increase in the gate current due to hole trapping, followed by a fall due to electron trapping; and over that timeframe there is also a decrease and a subsequent recovery in the threshold voltage, driven by these changes.

Further investigations, considering different stress voltages, revealed that hole trapping only takes place at gate fields in excess of 8 MV cm-1. The team from onsemi also determined that there is no hole de-trapping at 0 °C, and there is some electron de-trapping at 175 °C.

Drawing these findings together, Moens concluded that for high gate voltages, corresponding to a gate field of more than 8 MV cm-1, changes in threshold voltage determine the safe-operating area. But at the ‘use’ gate voltage, which is set by electron trapping, the change in threshold voltage is less than 1.2 V over 20 years, and t0 should be used to define the safe operating area.

This insight into how to best to describe the working life of the SiC MOSFET, along with the findings provided by NIST and ABB, show that there’s still a long way to go to refine the way we characterise and assess SiC devices. Progress is highly valued, as it will help to accelerate the shift from SiC to silicon power devices, by equipping engineers with the confidence that they understand the superior alternative, and know what to expect from it for many years.