Turbocharging the GaN MOSFET with a HfO₂ gate

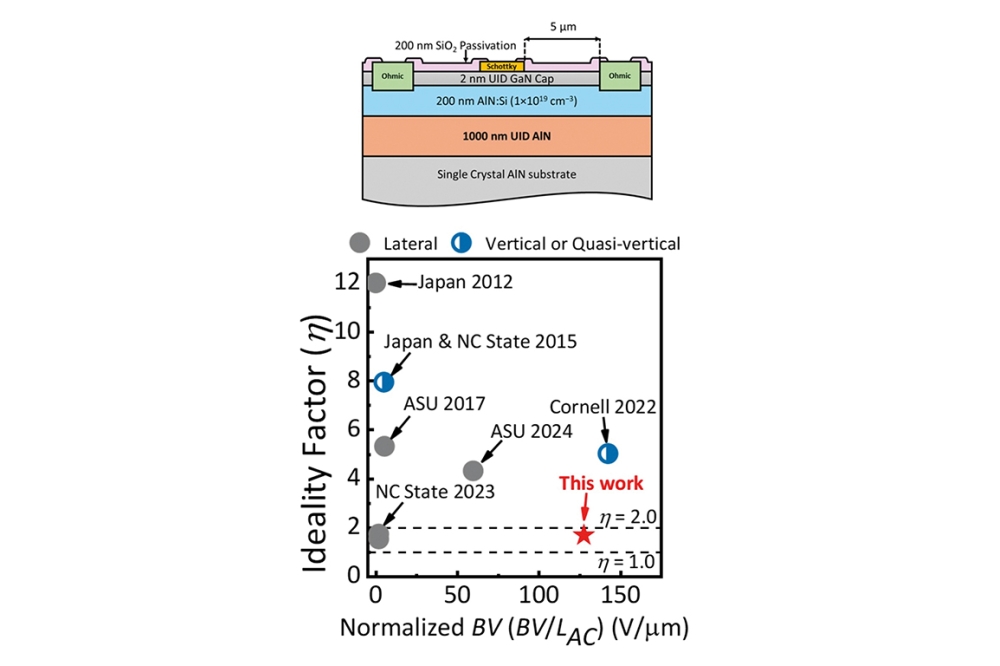

Researchers from Sandia National Laboratories, Albuquerque, have delivered a dramatic improvement in the performance of vertical GaN MOSFETs through the introduction of a HfO2 gate dielectric.

This team’s 1.2 kV MOSFET delivers an output current density of 330 mA mm-1- more than ten times that of the highest values reported for 1.2 kV-class GaN and SiC MOSFETs). This is alongside record setting performance for HfO2-on-GaN demonstrating a leakage current for the HfO2 film of just 0.5 nA at 2 MV cm-1, and a dialectric breakdown strength of 5.2 MV cm-1.

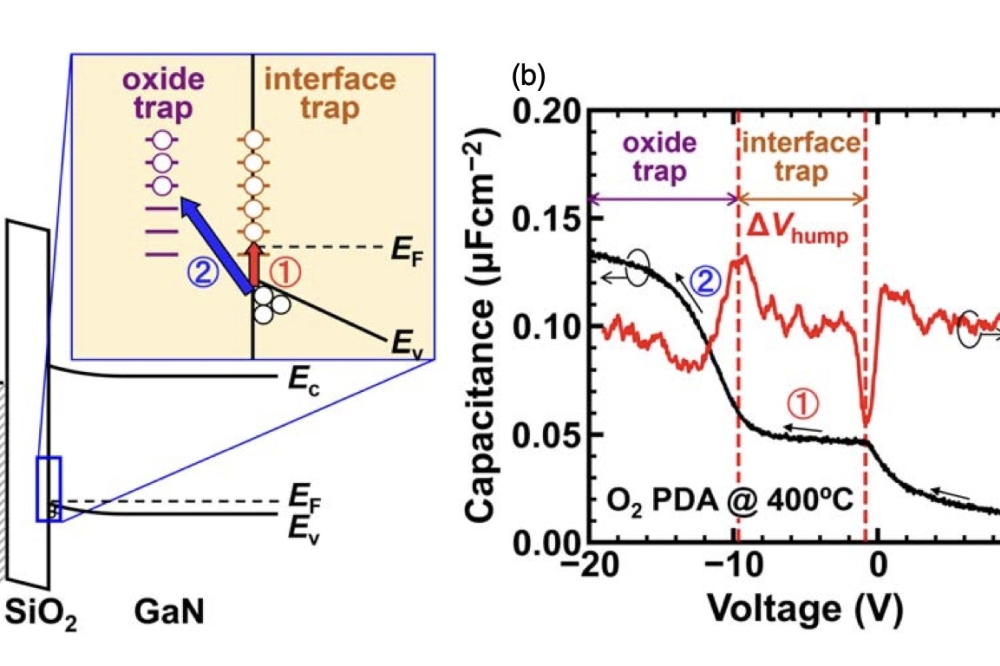

Team spokesman, Andrew Binder, told Compound Semiconductor that for many years it has been assumed that high-k dielectrics, such as HfO2, are not suited to wide bandgap semiconductors, due to the low band offset and an associated leakage current.

“This work demonstrates that given the right conditions it is possible to get low leakage and good film properties, despite the low band offset,” claims Binder, adding: “This also poses an interesting question, if it can be done on GaN, could it be done on SiC?”

Binder and his co-workers believe that the biggest contributor behind the hike in current density is the higher permittivity of the dielectric, which ensures a decrease in channel resistance. “Compared to SiC MOSFETs with an SiO2 insulator, our HfO2-gated MOSFET has a factor of five increase in permittivity.”

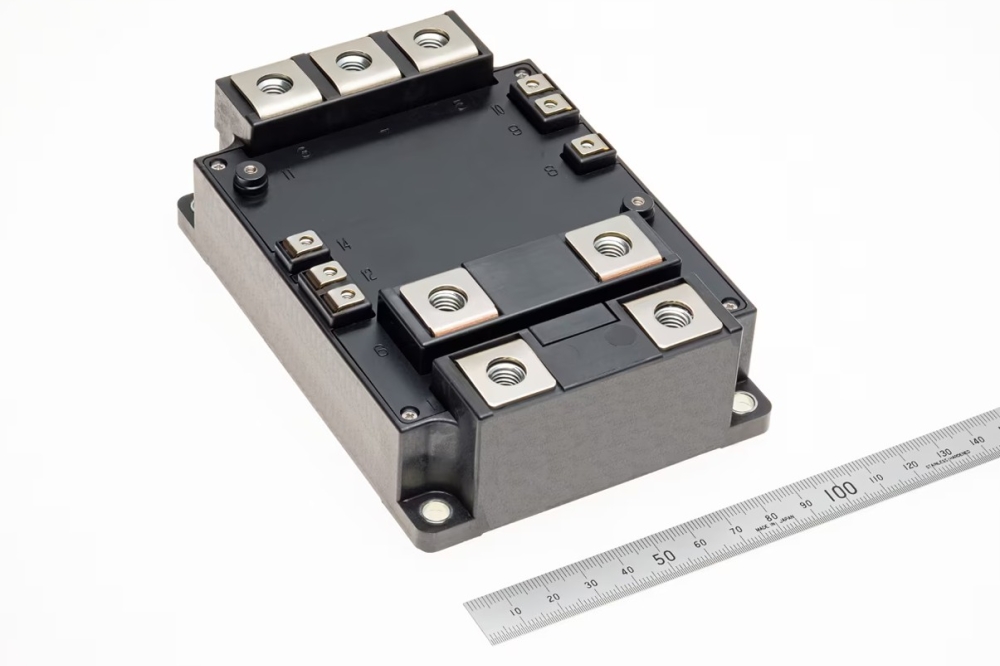

When the impact of a higher permittivity is considered alongside additional factors, such as a higher channel mobility and a channel length that’s shorter than SiC D-MOSFETs, one can start to explain the ten-fold hike in current density. This could be a game-changer in the power electronics industry, where there is much demand for 650-1200 V SiC MOSFETs from makers of electric vehicles.

In this voltage class, channel resistance is a significant limitation to device performance, so the substantial reduction realised by the Sandia team could enable a significant competitive advantage for chipmakers that incorporate their technology.

“Another consideration is that a significant reduction in on-resistance means that for the same current rating each die becomes smaller, which means the cost-per-die decreases, as there are now more die per wafer,” adds Binder.

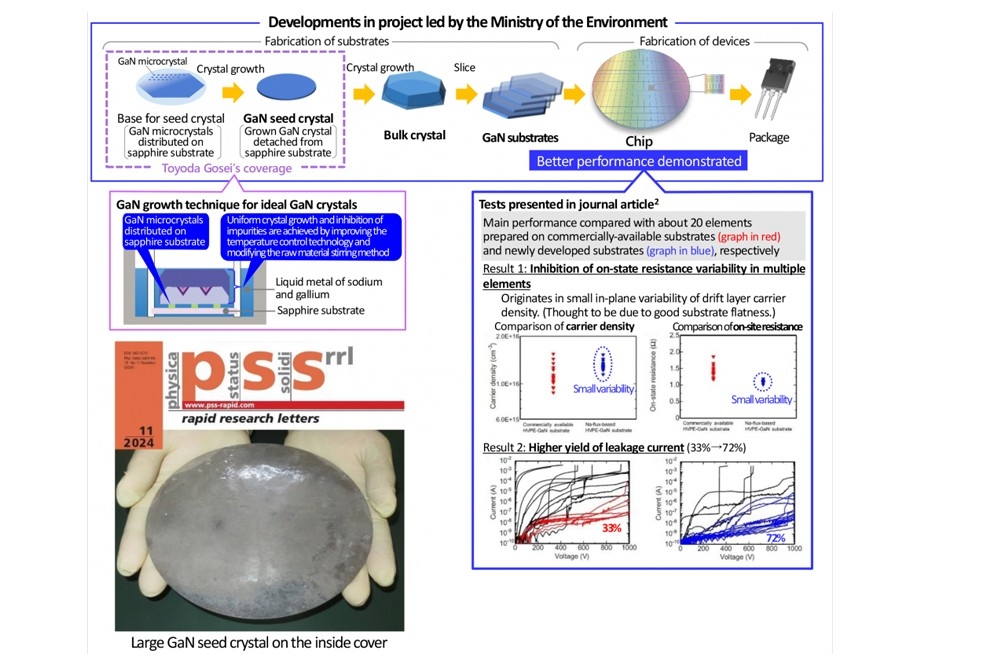

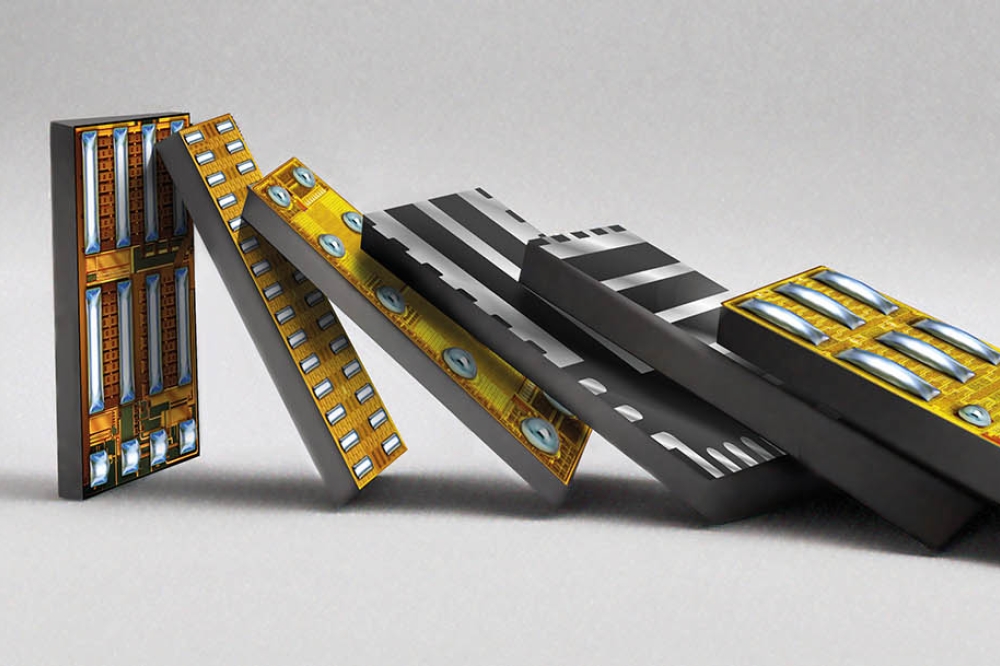

He and his co-workers produced their devices by loading an n-type free-standing GaN substrate from Mitsubishi Chemical Corporation into an MOCVD reactor and depositing a 12 µm-thick drift layer, followed by a 0.5 µm-thick p-body and a 0.25 µm-thick source layer. Etching followed to define the trench, body and junction termination extension. Prior to addition of the gate dielectric, the team prepared the surface with ozone treatment and a piranha clean, and activated dopants via annealing.

The team turned to a Savannah S100 reactor operating at 150 °C to deposit a 100 nm-thick layer of HfO2, using 960 atomic layer deposition cycles, before adding source, gate and drain contacts.

Electrical measurements on vertical GaN MOSFETs revealed a current density of 330 mA mm-1 at a drain bias of 5 V, and a positive threshold bias of 3.5 V. Specific on-resistance is 8 mΩ cm2, but could fall to just 1.1 mΩ cm2 by scaling the cell pitch from 70 µm to 10 µm.

Binder and co-worker are keen to explore the possibility of replicating their success with HfO2 on a SiC transistor. “Vertical gallium nitride is still a relatively immature platform for device development,” says Binder, who points to a very mature, established commercialisation path for SiC MOSFETs. “If we can demonstrate HfO2 on SiC successfully, then we have a quicker path to market than we do with vertical GaN.”

Reference

A.Binder et al. Appl. Phys. Lett. 17 101003 (2024)