Controlling threshold voltage instabilities in SiC MOSFETs

System designers can now benefit from new test and stress procedures for

SiC MOSFETs that realistically determine their worst-case threshold

voltage variations.

BY THOMAS AICHINGER FROM INFINEON TECHNOLOGIES

One of the greatest strengths of the SiC power MOSFET over its silicon-based equivalent is its capability to operate at much higher switching frequencies and lower losses. Thanks to this, engineers can build advanced power electronic circuits that feature smaller cooling units and smaller passive components. These gains are so highly valued that as well as opening up new applications, they are enabling SiC MOSFETs to replace silicon counterparts in existing applications, where new ground is being broken for lighter, more efficient system design.

When engineers design circuits with SiC components, they expect that as well as exploiting the performance benefits, they will not be held back by any compromise in quality compared with silicon counterparts. There is an expectation from these engineers of a predictable electrical parameter stability over lifetime.

Unfortunately, until fairly recently the initial general impressions of these engineers had been that SiC technologies are not quite there. There were concerns, for instance, regarding so-far-unknown threshold voltage (VTH) peculiarities, and their extraordinary electrical parameter drifts during reliability investigations. Scientific papers had shown large VTH variations within short periods of stress, raising concerns that critical electrical parameters of SiC MOSFETs were highly variable, threatening to get out of control during operation in the field, sooner or later.

Until recently, the origin and the application relevance of these short-term VTH instabilities in SiC MOSFETs had not been fully understood, with literature reporting a wide range of parameter variations. Various possible reasons have been proposed. One is that first-generation products had varied levels of quality; and a second is that fundamental issues hampered stable, reproducible measurements of crucial electrical parameters, such as the threshold voltage.

Recently, this second issue has been addressed by the release of new measurement guidelines for evaluating the VTH in SiC MOSFETs, published by JEDEC and drawing on contributions from our team at Infineon. We have gone on to develop a deeper understanding of the trapping dynamics at the metal-oxide semiconductor (MOS) interface. Outlined in this first section of this article, this insight has helped us to adapt VTH measurement routines so that they resolve the issue of undefined and non-reproducible measurements.

With a reproducible and reliable VTH measurement procedure at hand, we have made further strides, finally quantifying the effect of electrical stress on the condition of a device in a standardised way. This has been most valuable in dispelling major doubts surrounding the overall stability and controllability of SiC MOSFET technology. Our findings include the revelation that the mysterious short-term VTH variations are fully reversible and recur in every single switching cycle. Note that this effect, found in all SiC MOSFETs in the market and already present in pristine devices, is not a cause for alarm: it is an inherent device characteristic, rather than a reliability-critical degradation mechanism.

Figure 1. An illustration of threshold voltage dynamics of a SiC MOSFET

when switching the gate of a pristine SiC MOSFET in bipolar mode.

Our next important step has been to discover how to stress SiC devices in the most realistic way, so that we can determine worst-case VTH variations after the MOSFET has been used in an application for its intended lifetime. Historically, the approach that’s been applied to silicon power MOSFETs to check for systematic VTH variations is to raise these devices to an elevated temperature and perform static stress tests at a constant positive or negative gate bias. For high-temperature gate-bias tests, one would tend to select a stress temperature and bias higher than the use conditions, in order to cover the chip’s entire lifetime within a 1000-hour (typical) qualification test. The result produced by this test has always been considered to be the worst-case scenario. It has been assumed that a common alternative – the more application-near, gate-switching stress test – is less critical, because it may involve some compensating drift effects and recovery phases in between. We question that assumption with work showing that these factors do not apply to SiC MOSFETs. These findings are described in the second section of this article, along with our completely new stress

procedure.

Threshold voltage peculiarities

A stable and reproducible measurement of VTH is important. It’s needed to define the datasheet values of pristine devices and it’s mandatory for assessing VTH evolution in a stress experiment. In silicon MOSFETs this task is straightforward – it does not require any particular precaution. Pristine silicon power transistors always show the same VTH.

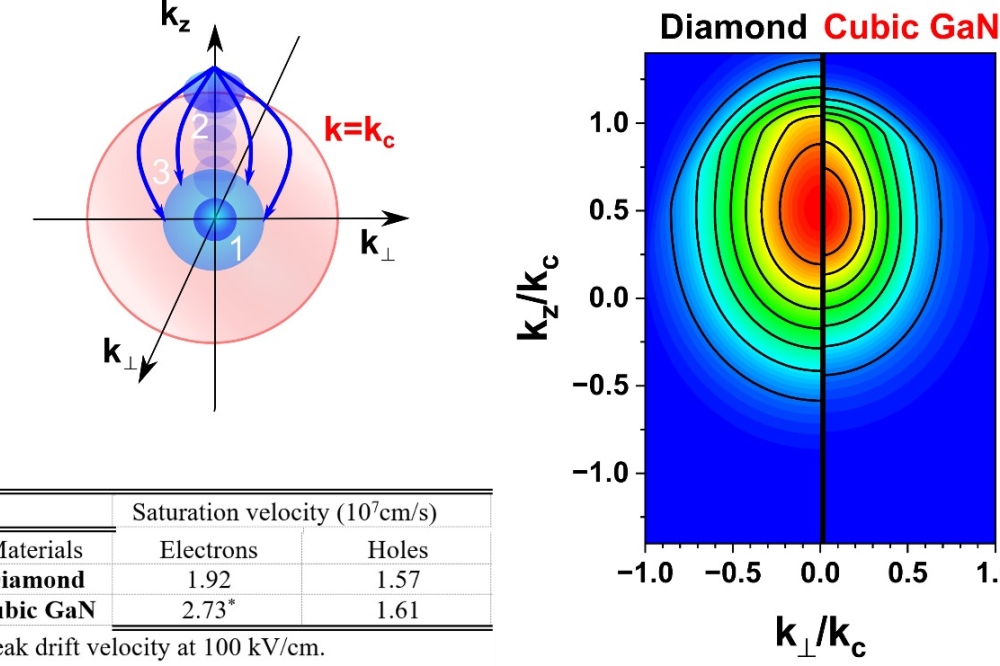

That’s not the case, though, in SiC MOSFETs, which have a VTH that’s not constant. According to our measurements, the VTH shows different values when the transistor turns on, coming from a negative gate voltage; and when it turns off, coming from a positive gate voltage (see Figure 1). This indicates that there’s a need to define the VTH hysteresis: it is the difference between the VTH during turn-on, the so-called upsweep VTH (VTHUP); and VTH during turn-off, the so-called down sweep VTH (VTHDOWN).

Hysteresis is at its largest when sweeping the gate between deep accumulation and deep inversion, for example, between -10 V and +15 V (this is illustrated in Figure 2, which shows typical transfer characteristics of SiC MOSFETs for fast upsweeps and downsweeps of the gate voltage). Hysteresis reduces when the upsweep starts at voltages closer to 0 V, and when sweeping is slower.

Figure 2. Transfer characteristics vary during turn-on and turn-off. VTH

is lower during turn-on due to holes captured at negative gate bias.

During turn-off, VTH is higher due to electrons captured at positive

gate bias. Hysteresis reduces when the upsweep starts at gate voltage

levels closer to 0 V, because fewer holes are trapped during the

negative gate voltage period.

Our investigations suggest that these effects are due to short-term charging and discharging of pre-existing traps located near to or directly at the SiC/gate-oxide interface. We have determined that the upsweep VTH is always lower, because the interface is charged positively in the negative half period of the gate pulse, due to holes captured from the valance band. Meanwhile, the down sweep VTH is always larger, because the interface is charged neutrally or even negatively in the positive half period of the gate pulse, due to electrons captured from the conduction band. There is actually a continuum of possible VTH values within the hysteresis envelope, arising from the large variety of capture and emission time constants for trapped charges in the virtually continuous defect band.

One consequence of these findings is that the ‘gate biasing history’ of the MOSFET can impact VTH measurements for a very long time. For instance, when the device is either floating, or biased at VGS = 0 V after the application of a positive or negative gate pulse, charges that are trapped near the mid-gap may be ‘stored’ at the interface for hours, days or even longer – this keeps the device in a state of non-equilibrium. This is a consequence of large thermal emission barriers, associated with the large bandgap of SiC. There’s no similar effect in silicon MOSFETs, because they have a lower density of interface traps and a narrower band gap.

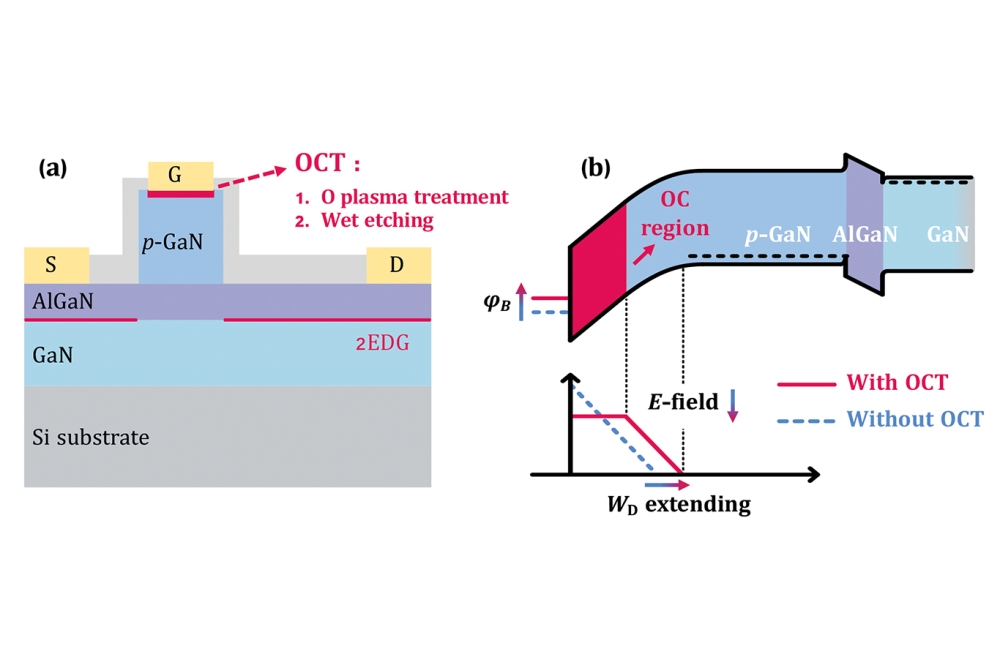

Based on these findings, we knew that the key to accomplishing a reproducible VTH measurement with a SiC MOSFET was to begin by defining a ‘gate biasing history’. One option is to apply a short positive gate pulse to the device, using gate voltages between the recommended use voltage and the maximum allowed voltage in the datasheet (see Figure 3). We call this technique gate conditioning. Once undertaken, VTH must be measured with a constant time delay.

Figure 3. An example of gate conditioning. Before measuring the VTH, a

positive gate pulse is applied for several milliseconds to bring the MOS

interface to a defined charged state. Afterwards, a VTH spot

measurement is performed using, for instance, a gated-diode biasing

scheme. To ensure reproducible results, there must be a constant time

delay between the conditioning pulse and the VTH measurement.

An easy way to accomplish fast, well-timed VTH spot measurements is to use a gated-diode measurement scheme. Here, the gate and drain terminals of the device are shorted, the source terminal grounded, and a threshold current, for example 1 mA, forced. Eventually, this gate conditioning procedure creates a defined, reproducible charge state at the SiC/gate-oxide interface, and enables a defined, reproducible VTH measurement. Our own research that is consistent with recent guidelines published by JEDEC has shown that more complex conditioning procedures, involving negative and positive gate conditioning pulses, also allow for reproducible measurements of hysteresis.

Having crossed the hurdle of measuring VTH in an accurate and reproducible manner, we took on the next challenge: controlling and assessing VTH instabilities in SiC MOSFET operations, by developing a stress procedure for determining worst-case VTH drifts for different application profiles.

Worst-case threshold voltage drifts

Quality is the ability to deliver what is promised. It follows that to realise the highest quality levels and secure reliable operation of SiC MOSFETs in different applications and/or mission profiles, it is crucial to know the worst-case change in VTH and other related electrical parameters over lifetime. Armed with such insight, system design engineers can consider potential variations in electrical parameters.

The most direct way to determine the variation in electrical parameters during real operation is to run full application tests and measure the condition of devices within their specified lifetimes. However, this is impractical in most cases. That’s because it would be too time consuming to come to a final result, and the variety of possible applications would be far too large to be checked in individual long-lasting application tests.

To ensure quality management while employing a practical approach, best practice is to select worst-case stress conditions and strive for stress procedures that are simplified but do not alter the degradation mechanism of interest. One of the merits of this is that all allowed application conditions are covered by one stress test. There may also be an opportunity to turn to simplified stress procedures, which might offer some potential for acceleration and parallelization.

Another way to look at this is that the ideal stress procedure should encompass all important stressors addressing a certain application-relevant degradation mechanism, but at the same time be devoid of application conditions that do not impact the final drift result, or hinder upscaling of sample size and acceleration of stress. To uncover such a unified stress procedure, we have found that it’s been useful to look at common aspects of different SiC MOSFET applications and identify the main stressors.

When SiC MOSFETs are used in switching applications, they are typically running at frequencies between 5 kHz and 500 kHz. As well as fast switching, there is often the need for a wide and flexible gate drive operation window, including margins for overshoots, undershoots, and negative gate turn-off voltages to allow safe turn-off. Due to this, over the lifetime of a SiC MOSFET, it is often exposed to a large number of bipolar gate switching events.

Based on the typical characteristics for a SiC MOSFET, it is expedient to stress this device in pulsed gate mode rather than DC mode when aiming to trigger the same degradation mechanisms that determine VTH instabilities in this transistor, when it’s deployed in real applications. Underlining this point are recent discoveries by our team, and also academic researchers working independently in China, that SiC MOSFETs show different and even enhanced parameter instabilities under bipolar gate switching conditions compared with static gate stress. This mechanism is called the gate switching instability.

Another key finding from this body of work is that for any given gate switching condition, the resultant threshold voltage drift depends predominantly on the number of gate switching events (see Figure 4). Consistent with our findings, a team in China has later independently confirmed that the total stress time and the frequency of the duty cycle is of minor or even of no importance. Drawing on this finding, it has been revealed that it is possible to determine the time evolution of VTH, for a given application profile, by simply stressing devices up to their maximum number of gate switching cycles. We have shown that this can be accomplished using elevated stress frequencies of up to 2 MHz for acceleration.

Figure 4. An exemplary threshold voltage drift after 1011 switching

cycles, using stress frequencies between 70 kHz and 2 MHz. The resulting

VTH drift after the same number of switching cycles is virtually

identical despite the different total stress times.

To cover all possible applications, devices must be stressed to their worst-case conditions, using the most critical operating conditions allowed in the datasheet. This means using VGS,max and VGS,min. Taking this approach also exposes overshoots and undershoots in the gate signal that may occur in the application and influence gate switching instability.

We have found that devices from different manufacturers behave differently when stressed at different temperatures. Some SiC MOSFETs drift more at lower temperatures while others drift more at higher temperatures. Due to these variations, it is far from obvious which temperature is really the worst-case for devices from different manufactures.

Through collaborative efforts, we have tested two more potentially application-relevant stressors: the drain voltage and the load current. This study revealed that neither led to altered VTH instabilities. It’s a negative result that is extremely beneficial, because it allows a drastic simplification of the stress procedure without neglecting any important VTH stressor present in real applications.

Using a stress frequency of 500 kHz and maximum data sheet conditions for gate voltage and temperature, we have undertaken measurements that led to the plotting of an exemplary VTH drift evolution curve (see Figure 5). The total stress time is 7000 hours, with stress interrupted multiple times to record the VTH using the gate conditioning approach described previously. The slope of this VTH drift evolution curve is higher for fewer switching cycles (< 1011 cycles), and tends to saturate when exceeding 1011 – 1012 switching cycles.

To assess the worst-case drift at the end of an arbitrary application profile, one must calculate the total number of gate-switching events, before either interpolating or extrapolating the VTH drift evolution curve. This curve can also be used to calculate variations in other related electrical parameters, such as the on-resistance. In that case, it’s worth noting that changes in VTH predominantly affect the channel resistance as a component of the total on-resistance of a power device. Other components of resistance, such as those associated with the JFET, the drift zone and the substrate, are not affected by VTH instabilities.

Figure 5. Example of worst-case VTH drift evolution curve due to gate

switching stress. This measurement has been made at the maximum data

sheet conditions and 500 kHz. The bold dashed line (black) indicates the

power law fit of data points in the saturation regime, but within 1000

hours of total stress time, corresponding to around 2 x 1012 cycles.

Additional data points recorded up to 7000 hours of stress time (>

1013 cycles) confirm the validity of

the power law fit.

In application notes, our company has published parameter drift evolution curves that are similar to those shown in Figure 5. Drawing on this information, our customers are able to directly extract the maximum drift that can be expected for a given technology during a specific application. For instance, for automotive drive applications, the total number of switching cycles until the end-of-application profile is relatively low, typically around 1011 cycles. This allows the maximum VTH drift to be directly read from raw data, shown in Figure 5.

However, for solar applications, which feature operation under frequencies of typically 70–100 kHz during daylight hours for 20 years or more, data must be extrapolated, because a real end-of-application profile test would lead to an unreasonably long stress time. The curve to be used for this power law extrapolation is shown in Figure 5.

In short, drawing on our efforts to increase our understanding of trapping dynamics at the SiC/gate-oxide interface, we have gone on to develop new characterisation and stress procedures that are tailored to the characteristics of the SiC MOSFET.

These new methods provide standardized, reproducible measurements, as well as realistic assessments of time-dependent parameter variations in real applications. In turn, this allows engineers to predict how device characteristics will evolve during an application, and paves the way for SiC MOSFETs to reach their next level of quality excellence.

Further reading

† T. Aichinger et al. “Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs” Microelectron. Reliab. 80 68 (2018)

† K. Puschkarsky et al. “Understanding BTI in SiC MOSFETs and Its Impact on Circuit Operation,” IEEE Trans. Device Mater. Reliab. 18 144 (2018)

† JAP183, “Guidelines for measuring the threshold voltage (VT) of SiC MOSFETs”, www.jedec.org

† JAP184, “Guideline for Evaluating Bias Temperature Instability of Silicon Carbide Metal-Oxide-Semiconductor Devices for Power Electronic Conversion”, www.jedec.org

† P. Salmen et al. “A new test procedure to realistically estimate end-of-life electrical parameter stability of SiC MOSFETs in switching operation”, IEEE International Reliability Physics Symposium (IRPS) (2021)

† H. Jiang et al. “Dynamic gate stress induced threshold voltage drift of silicon carbide MOSFET”, IEEE Electron Dev. Lett. 41 1284 (2020)

† X. Zhong et al. “Bias Temperature Instability of Silicon Carbide Power MOSFET Under AC Gate Stresses,” IEEE Trans. Power Electron. 37 1998 (2022)

† M.W. Feil et al. “On the Frequency Dependence of the Gate Switching Instability in Silicon Carbide MOSFETs”, Proceedings ICSCRM, Davos, 2022

† M. Sievers et al, “Monitoring of parameter stability of SiC MOSFETs in real application tests”, Microelectron. Reliab. 114 113731 (2020)

† Infineon Application Note 2018-09