Superjunction sparks super devices in silicon carbide

Armed with a clever charge-balance structure, SiC power devices are pushing beyond their limit.

BY JAN CHOCHOL AND ROMAN MALOUSEK FROM ONSEMI

The entire power electronics industry is buzzing with SiC activity. It’s no wonder, given that SiC devices have a dielectric breakdown field strength that’s ten times higher than that of silicon, as well as twice the electron saturation velocity of the incumbent, three times its bandgap, and a thermal conductivity that is better by a factor of three. All high-power applications benefit from these traits, shown in Figure 1, so it’s of no surprise that vendors, fabs and OEMs are embracing the rapid adoption of SiC. All are trying to outperform, outlast and outclass their competition.

Figure 1. Areas of application for different power electronic technologies.

Due to all this frenetic activity, there is some turmoil in this sector, creating opportunity for all kinds of development. This has motivated our team at onsemi to explore various concepts. Against the backdrop of a maturing SiC industry, we have been able to revisit some topics that just a few years ago would be either unfeasible, too expensive or just plainly not possible with the toolset available at that time.

One such concept is the superjunction. Regardless of design, any device that is made from SiC will benefit from its unique properties. They include a large electric breakdown field that shaves tens of micrometres of epi thickness, greatly reducing the on-state resistance for a given voltage rating compared with silicon. But with the superjunction structures that we have explored, one can go a step further. Generally, this structure consists of alternating regions that are highly doped, tightly spaced and with equal and opposite doping – an architecture that ensures charge balancing. With such a structure, the high doping results in superior conduction that reduces resistance. But that’s not the only benefit we get – operated under reverse bias, the superjunction is fully depleted, with the electric field spread evenly in a roughly rectangular shape. Thanks to this, compared with a classical unipolar drift region, where the electric field must be trapezoidal (see Figure 2), we realise a higher breakdown field at the same drift thickness.

Figure 2. Schematic diagram of JBS diode with unipolar drift region (left) and superjunction JBS diode (right).

The real question is how can we make such a structure? We need to have defined pillars, with a controllable concentration reaching several micrometres below the surface. As each micron of superjunction depth can block about 200 V (we go on to show this), a 1200 V device needs more than 6 μm of well-controlled superjunction pillars.

One option for forming the pillars is ion diffusion. However, those working in the SiC community don’t tend to concern themselves greatly with this technique, as there is simply no way to diffuse ions in SiC. This has led some groups and companies to try other approaches, such as trench filling by CVD.

Revisiting ion implantation

But in our pilot study, we decided to take another look at ion implantation, due to the simplicity of the method and the availability of tools. We have investigated two different techniques. One involves using very high energy implants. Roughly speaking, this is a brute force approach; we push the implants deep into SiC, due to their high kinetic energy. Higher energy means deeper penetration. Then, using multiple implants, we can chain the concentration profile together to create a seemingly uniform distribution. The caveat of this approach is that we have to shield the other pillar from the implantation. So one implant can be blanket, while the other must be masked and have twice the dose of the other. Success is not easy, as there is only so thick a photoresist that can block the implant.

Figure 3. JMOL simulation of 4H-SiC lattice. Blue arrow shows the

direction of c-axis of the crystal. (a) view through the channelling

direction; (b) sideview; (c) tilted lattice; (d) tilted lattice

sideview.

Due to this limitation, we have also explored the channelled implant. One key characteristic of the 4H polytype of SiC, used for power applications, is that it permits ion implantation along a preferential angle, where ions ‘see’ through the lattice and the number of ion-lattice collisions plummets. This principle, illustrated in Figure 3, leads to a concentration profile that is far deeper and flatter than that normally possible with a random implantation direction. For example, a 900 keV non-channelled implant of aluminium reaches a depth of up to 0.7 μm, while channelling with this energy extends the depth to 3 μm.

With this approach we have produced pillars by combining a blanket high-energy nitrogen implantation, which does not require a mask, with a masked channelled aluminium implantation. The success of this scheme is seen in profiles obtained by secondary-ion mass spectrometry (see Figure 4).

Figure 4. SIMS data on implanted profiles in the superjunction experiment.

The channelled direction is along the 0001 direction of the crystal – this is also the direction in which the crystal is grown. As most commercial SiC crystals are cut at a 4 ° angle, this is the channelling angle we employ. To produce well defined pillars, it’s critical that the implantation tool maintains the optimal angle across the wafer and batch-to-batch. We’re grateful for the support of Nissin Ion Equipment, which helped us in this endeavour during our pilot study.

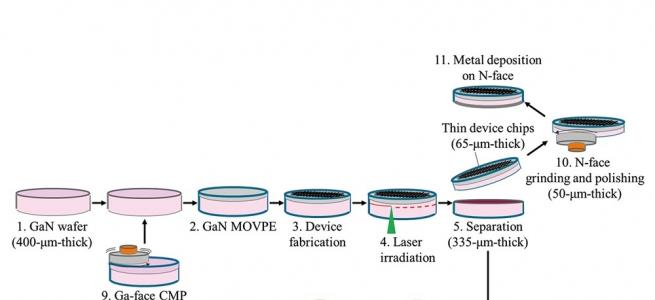

Regardless of whether we employ channelling or very-high-energy implantation, an epi re-growth step is needed to get to the desired thickness. When restarting the epi process for each new pillar layer, we tuned the conditions carefully, to minimize any potential loss of implanted material (etch back) and ensure a constant concentration throughout the epi-structure. Another challenge we have faced is to tune the alignment of the masks to the alignment marks after each epi regrowth, and to renew the marks to assure a precise position of the layers that follow. For the structures formed by very high energy implantation we undertook three epilayer growth steps, each involving a deposition of a 1.2 μm-thick layer; and for the channelled run, we used just two growths, each 2.45 μm thick. We have fabricated junction barrier Schottky diodes from both types of structure. This involved using parallel stripes as mask for the pillars. As these stripes are parallel to the wafer flat, we avoid mask shadowing when undertaking channelled implantation.

Assessing different die

To fully assess our device’s behaviour, we have made both small (0.0012 cm-2) and large (0.018 cm-2) dies. Small dies allow us to investigate a multitude of designs, while their large siblings have properties more akin to production-line devices. With superjunction devices, it is essential to ensure a proper charge balance. This means that both pillars have the same concentration of dopants. With any process, factors are at play that will lead to a spread in the concentration. But it is possible to address this by varying the stripe width, as this provides a mechanism to compensate and tune the design – a wider, lower-doped pillar will behave the same as a narrower, higher doped one. We implant the top of the p-type pillar with a shallow, high dose of aluminium to ensure a good ohmic contact.

Contacts to our devices have been made with a standard SiC process. This added a Ti/TiN Schottky/ohmic contact to the front side. We turned to a backside grind and metal deposition for the cathode contact. Our devices feature termination, used to spread the electric field and distribute the avalanche current homogeneously in an active region. We verified this had been accomplished by electroluminescence, which shows a uniform breakdown in the active structure (see Figure 5).

Figure 5. Left: Schematic of the device design. Right: Electroluminescence of the device in the avalanche breakdown.

Before diving into the results of our superjunction study, it is worthwhile to consider our assumptions of the expected behaviour. Key characteristics are the breakdown voltage of the diode and its on-state resistance. The ideal is to have a perfect 1:1 ratio in pillar concentrations, as this ensures a maximum achievable breakdown voltage – for a given thickness of the superjunction. Meanwhile, the on-state resistance scales linearly with the n-type concentration, where the conduction happens (behaviour is illustrated in Figure 6).

Figure 6. Predicted behaviour of the superjunction device.

The actual results of our study, shown in Figure 7, confirm our assumptions. We used three wafers for each implantation scheme, each with a slightly different dose (± 10 percent), and changed pillar ratios in the device design. Our breakdown results follow a parabolic shape, with the absolute position determined by the thickness of the superjunction. Note the spread across the wafer, with a thicker epi-structure near the flat giving a higher breakdown voltage (optimizing for uniform wafer distribution was not part of the study). As expected, the on-state resistance increases with the width of the p-type pillar and with the epi-thickness. We have addressed the variation in the on-state resistance between the wafers to the variation of the substrate resistance.

Figure 7. Electrical data from characterization of the superjunction devices characterization of the superjunction devices

To compare the results realised by very-high-energy implantation and channelling, we have normalized breakdown values by thickness. After omitting the epi-thickness spread, both approaches gave about 210 V/μm of breakdown. This is a crucial finding, implying that both approaches are equal, in terms of electrical performance and process stability. Where the differences lie are in the toolset needed and the number of epi steps required.

With data at hand, we can compare our devices to those with a classical architecture, including a variant with a unipolar drift region. Our evaluations, which include a plot of the one-dimensional theoretical limit of such a device, enable comparison of on-state resistance and breakdown voltage (see Figure 8). We see that with our test devices, measurements on our larger die show that we are just at the tipping point at 1000 V/0.7 mΩ cm-2. Generally, the sweet spot for usage of superjunction devices is above that, in the 3 kV-5 kV region.

Figure 8. Trade-off curves of breakdown voltage and on-state resistance

for unipolar and superjunction devices with experimental data shown

This, though, is only one side of the equation. SiC devices are also sought after for their high-temperature performance, which comes in to play in almost all their applications. It is here where the superjunction puts the ‘super’ in devices. The drift region, where the blocking field is spread, is the lowest doped part of the device. It is here where there is a large contributor to device resistance – but the introduction of the superjunction makes this region thinner and highly doped, changes that as we’ve seen pay off after 1000 V of blocking voltage.

Thanks to high doping in this region, this device is less affected by a temperature-induced resistance increase. What happens is that the device maintains its low resistance even at higher temperatures. All the while the breakdown is largely unaffected. In fact, it increases, due to increased phonon scattering – more energy is needed to push electrons into avalanche. So, as we’ve shown, replacing the drift region with the superjunction pays dividends, transforming an ordinary device into one that excels in highly demanding applications.

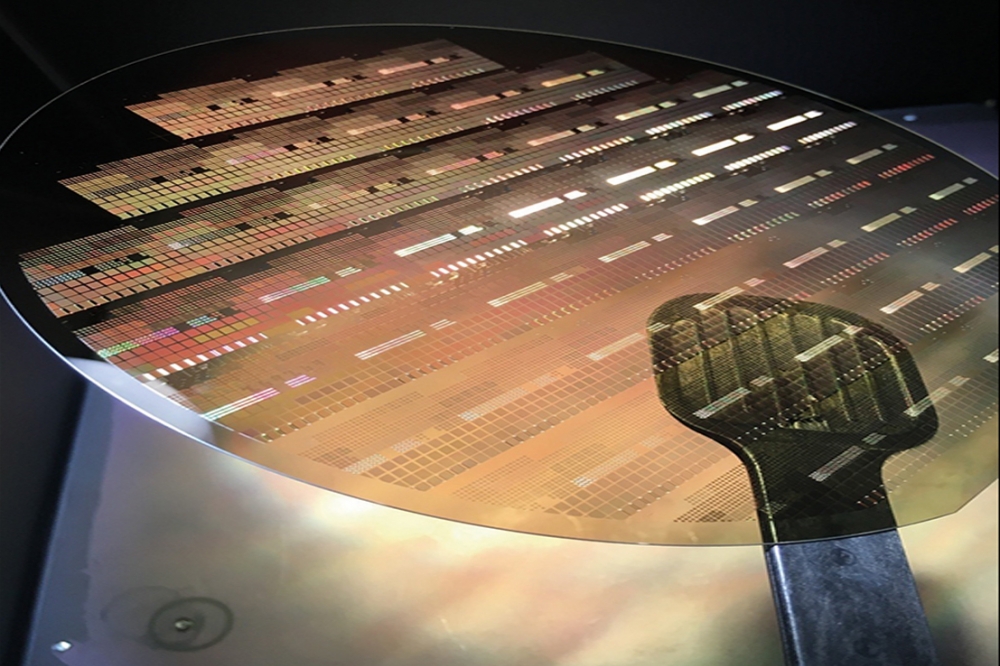

The adoption of SiC devices and their related development, including the progress reported in this study, would not be possible without scaling up the entire SiC ecosystem. Whether it is the making of substrates, involving wafering, grinding, polishing; or epitaxial growth or other front-end or backend processes; every step is a demanding operation that needs to draw on hard-earned expertise and specialized tools.

SiC initially came to us at onsemi through the acquisition of Fairchild, where device technology has ever since been developed in close cooperation between: the design center in Kista, Sweden; the device and process integration teams in Bucheon, Korea; and the engineering team at South Portland, Maine, responsible for developing SiC epi technology.

Our current role includes supporting SiC development and production in key fabs, in Bucheon, South Korea and in Rožnov pod Radhoštěm, Czechia. In Rožnov, which is a small town nestled in the Beskids mountain range, materials development is gaining much attention, recognized with an award for the most innovative company in the region.

With the recent acquisition of a SiC substrate manufacturer – GT Advanced Technologies – our company has increased its level of vertical integration and solidified its SiC device portfolio. These moves have strengthened our position as a significant force in the power electronics industry and sharpened the cutting edge of SiC technology.