GaN RF HEMTs: Powering ahead with native substrates

GaN-on-GaN high-power amplifiers with through-substrate vias are

delivering record-breaking power-added efficiencies and continuous-wave

operation

BY NAOYA OKAMOTO AND YUSUKE KUMAZAKI FROM FUJITSU LIMITED

Electronic devices make our lives richer and more convenient. They are now taking us towards an advanced society, formed through the fusion of cyberspace and physical space. On entering this era, we will benefit from vast numbers of sensors in physical space collecting big data, quantitatively analysed by artificial intelligence in cyberspace. New value will be created from this, including the provision of high-quality services. Underpinning this new world order will be an increase in the use of radio waves above the microwave band to sense and collect data, alongside networks that exchange huge amounts of data, as well as sectors within industry that manufacture substances that bring new value. Supporting this introduction of a higher sensing resolution and a roll-out of a higher network capacity will be an increase in the frequency of solid-state power amplifiers deployed in radio equipment. A shift from microwaves to millimetre waves is already underway, and migration to the terahertz domain will follow.

Moving to higher frequencies is not trivial. Challenges are not limited to simply ensuring that devices can operate at higher speeds – there is also the issue of a reduction in the power conversion efficiency of solid-state power amplifiers at higher frequencies, leading to greater power consumption. This is at odds with a sustainable society, as to curb the carbon footprint of the communication sector, the power consumption of radio equipment must fall as the number of units increases.

The most efficient, powerful solid-state power amplifiers are based on GaN HEMTs. These RF transistors are typically fabricated on non-native substrates, such as SiC or silicon. However, the power and the efficiency of these devices are held back by electron traps that form in the GaN epilayers – mainly the buffer layer – and lead to current collapse.

Our team from Fujitsu, Japan, is tackling this issue head-on by switching the substrate to free-standing GaN. It is a solution we have been working on for many years. About ten years ago, when characterising the metal-insulator-semiconductor interface and the Schottky junction of GaN-based epitaxial layers grown on GaN substrates, we observed excellent crystal quality in this GaN-on-GaN heterostructure. But at this time only n-type, rectangular GaN substrates that were small in size were available. This restricted our development to the basic research phase.

Around 2017, when the availability of semi-insulating 2-inch GaN substrates began, we embarked on full-fledged work on RF GaN-on-GaN HEMTs. Initially, we directed our efforts at developing RF GaN-on-GaN HEMT power amplifiers for microwave heating. This project, supported by the Japan Ministry of the Environment, required transistors to run under severe conditions of high-power, continuous-wave operation. Realising success on these fronts would create a device that could serve in other applications, such as radar and wireless communication. However, progress would not be easy, due to the lower thermal conductivity of the GaN substrate compared with that made from SiC.

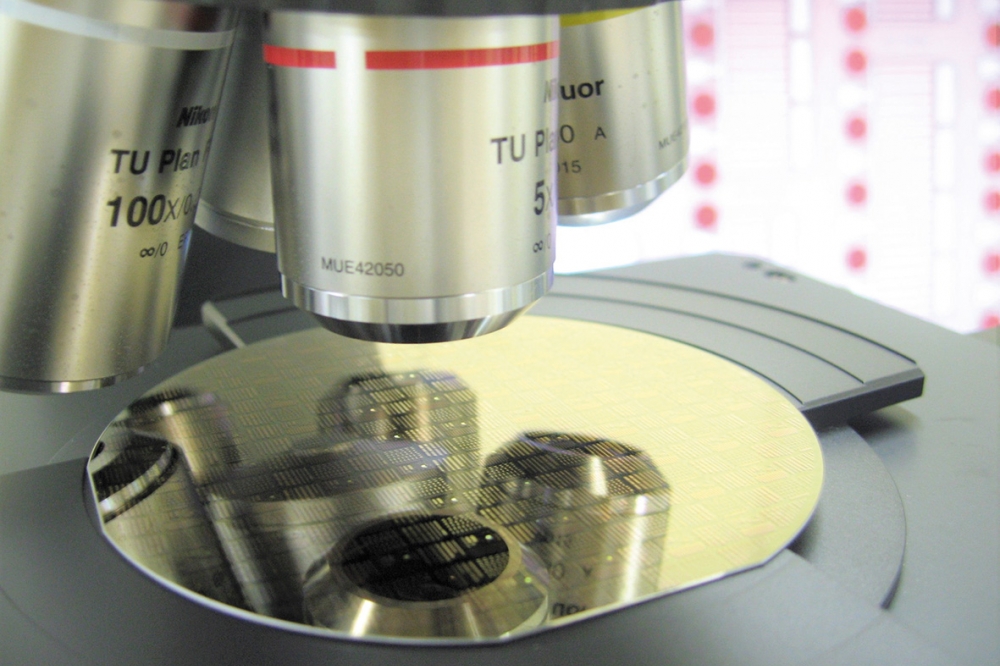

Figure 1. Fujitsu is a pioneer of the RF GaN-on-GaN HEMT power amplifier.

Recently, we have shown that this concern can be overcome by: increasing the power-added efficiency, through improvements to the GaN substrate/epilayer interface; and developing GaN through-substrate vias that reduce the source inductance (see Figure 1).

Targeting record-breaking efficiencies

As more efficient devices minimise self-heating, we decided to aim for a record-breaking power-added efficiency. Young researchers within our team spearheaded in this effort, leading the development of front-side devices for RF GaN-on-GaN. This project kicked off by comparing the quality of GaN epitaxial crystals grown on a conventional SiC substrate and on a GaN substrate (see Figure 2). Scrutinising these materials revealed a dislocation density in the GaN grown on SiC of 2×108 cm-2, compared with less than 106 cm-2 for GaN grown on a native substrate. In addition, HEMTs were fabricated from these epiwafers to obtain basic device characteristics. Results confirmed that GaN-on-GaN transistors have diminished current collapse compared with their GaN-on-SiC counterparts, due to superior crystal quality (see Figure 3). However, measurements of the power output at high frequencies were disappointing, with the power-added efficiency for GaN-on-GaN HEMTs buried within conventional GaN-on-SiC data.

How can it be that despite a far better crystal quality, the power produced by this native device is no better than that for a GaN-on-SiC HEMT?

Figure 2. Transmission electron microscopy underscores the superior material quality of GaN-on-GaN compared with GaN-on-SiC.

Figure 3.Pulsed current-voltage characteristics show that GaN-on-GaN

RF HEMTs suffer from less current collapse than those based on

GaN-on-SiC.

Investigations eventually revealed a conductive layer at the GaN substrate/epitaxial interface, stemming from silicon contamination. The level of silicon is not insignificant, having a concentration more than an order of magnitude higher than that of the iron concentration within the GaN substrate (see Figure 4). Note that a quarter of a century ago, a similar problem plagued GaAs substrates. Their surfaces can be riddled with the likes of silicon, carbon and oxygen, impurities activated by improvement of crystal quality through homoepitaxy. The young researchers in our team were unaware of this issue, as it had not been a problem when growing GaN epilayers, due to the use of non-native substrates. To address this issue, we turned to wet processing the substrate surface prior to epitaxial growth (see Figure 4). This approach reduced the silicon concentration to below that for iron, leading to suppression of the high-frequency leakage path. Thanks to this, we could realise a record-breaking power-added efficiency of more than 80 percent in the 2.45 GHz ISM-band (see Figure 5).

Figure 4. Secondary ion mass spectrometry (SIMS) showed that pre-treatment of the GaN substrate can prevent high levels of silicon contamination.

Figure 5. Supressing silicon contamination leads to a hike in the

power-added efficiency of discrete GaN HEMTs operating at 2-3 GHz.

The virtue of vias

Another important technique for improving the performance of power amplifiers based on the RF GaN-on-GaN HEMT is to add GaN through-substrate vias, as this reduces the source inductance. Taking this approach is not a novel – it is already applied to commercially available GaN-on-SiC devices. We have been working on this for some time, having started to develop through-substrate vias for GaN when we began device development.

Our efforts began by investigating GaN etching. Employing inductively coupled plasma etching, using a mix of chlorine and boron trichloride gases, we targeted an etching rate of at least 1 µm/min and an etching selection ratio of 30 or more, using a nickel metal mask. While success came relatively quickly, we still had challenges associated with the formation of pillars (see Figure 6).

Figure 6. Optical microscopy and scanning electron microscopy images (c)

and (d) show that switching from conventional conditions (a) to optimum

conditions (b) improves the etching of by-products.

Previous experience associated with SiC via hole etching had taught us that inclusions contained in the SiC substrate could impact pillar formation. To see if this issue remained with GaN, we scrutinised the bottom surface of these substrates with a scanning electron microscope. However, we failed to find any inclusions on GaN substrates grown by HVPE with void-assisted separation. Note that this might not be the case with GaN substrates grown by other methods, such as ammonothermal and sodium-flux – we simply don’t know.

We then focused on the wafer surface temperature during etching. Using almost identical plasma power conditions, we found that etching SiC involved a wafer surface temperature of 200 °C or more. In comparison, for GaN the temperature could be as low as 90 °C, making the etching by-product difficult to remove.

To address this concern by promoting the desorption of the etching by-product, we increased the wafer surface temperature by dialling back the cooling helium pressure. This action immediately solved the pillar problem (see Figure 6). With optimized etching conditions, we could successfully form a GaN via hole with a depth of 91 µm, using a GaN etching rate of 1.5µm/min and a selectivity to the nickel metal mask of 35.

However, another issue emerged: etching selectivity fell to one-third of that for conventional SiC etching, falling from a value of around 100 to about 35. The reduced selectivity impacted the thickness and the process for the front-side etch stop. Compounding matters, the remaining metal mask for via etching interfered with the stealth dicing of the GaN substrate. To overcome these problems, we refined our process for forming vias in GaN (see Figure 7).

Figure 7.A cross-sectional scanning electron microscopy image of a GaN through-substrate via of a GaN-on-GaN HEMT.

Upping the power

Thanks to this progress, we were now in a position to draw on all our development and integrate our technologies. Due to the lower thermal conductivity of GaN than SiC, we had concerns relating to heat radiation characteristics. Encouragingly, we could realise heat dissipation characteristics comparable to those for GaN-on-SiC by drawing on thermal simulation and introducing backside processing (see Compound Semiconductor 25 Issue 7, October, 2019, p32). But we were still to demonstrate GaN-on-GaN high-power amplifiers with output powers greater than 50 W.

Now this value has been exceeded with a GaN-on-GaN high-power amplifier featuring a through-substrate via, 36 gate fingers, a gate length of 0.5 µm, a unit gate width (Wgu) of 300 µm, a gate-to-gate spacing (Lgg) of 30 µm and a total gate periphery of 10.8 mm. This chip has a Wgu/Lgg aspect ratio of 10, creating a very severe condition for heat dissipation.

After mounting our chip on an evaluation board, we carried out large-signal measurements that produced an excellent set of results (see Figure 8). Driven in pulsed mode, using 10µs pulses and a 1 percent duty cycle, our amplifier delivered a maximum output power of 64.3 W and a peak power-added efficiency of 71.1 percent at 2.6 GHz. Running in continuous-wave mode produced a slight reduction in performance, due to self-heating, with values of maximum output power and power-added efficiency falling to 54.6 W and 63.3 percent. According to the simulated transient response, we think that the difference in channel temperature between continuous-wave and pulsed operation can be as high as 100 °C. However, the realisation of continuous-wave operation indicates that our GaN-on-GaN HEMT power amplifier has suitable heat dissipation characteristics, and eliminates concerns regarding this particular technology.

Looking ahead

Two of the biggest issues facing RF GaN-on-GaN HEMTs are the cost of these devices and the size of the substrate. Progress is being made with the latter: a 4-inch iron-doped GaN substrate has already been commercialized, and a 6-inch GaN substrate will soon be realized. Even so, prices are still quite high, and need to fall to at least the same level as SiC to enable the commercial launch of RF GaN-on-GaN HEMTs. Ensuring that this happens requires not only the efforts of substrate manufacturers, but also demand for power and optical devices, as well as RF devices.

Figure 8. Power characteristics of a GaN-on-GaN HEMT power amplifier in

pulsed (closed triangles) and continuous-wave (closed circles)

operation.

It is also anticipated that problems will arise in device manufacturing, along with the enlargement of the diameter. Our team is playing its part in addressing these important issues by starting to fabricate 4-inch RF GaN-on-GaN epiwafers. While the efficiency of the GaN devices decreases with increasing frequency, we expect that this decline can be suppressed with high-quality crystalline material. Devices featuring such epilayers are tipped to ensure ultra-high data rates for beyond 5G and 6G, realised by using GaN-on-GaN with ultrafine gates.

Another opportunity for improving device performance is to introduce architectures that combine the high crystal quality of GaN-on-GaN with materials with great thermal conductivity. Options for high-performing heat spreaders include diamond. However, its addition would need to be cost-competitive, just like the introduction of GaN substrates.

This research was partially supported by the Japan Ministry of the Environment, as part of the Project of GaN technology innovation for enabling decarbonized society and lifestyle.

FURTHER READING

Y. Kumazaki et al. Remarkable Current Collapse Suppression in GaN HEMTs on Free-standing GaN Substrates, BCICTS Conf.,

2019, 10b.2.

Y. Kumazaki et al. Over 80% power-added-efficiency GaN high-electron-mobility transistors on free-standing GaN substrates,

Appl. Phys. Express 14, 016502 (2021).

N. Okamoto et al. Backside Processing of RF GaN-on-GaN HEMTs Considering Thermal Management, CS ManTech Conf., April 2019, 10.5.

N. Okamoto et al. High-rate ICP Etching for GaN Through-substrate Via of GaN-on-GaN HEMTs, CS ManTech Conf., 2020, 8.1.

N. Okamoto et al. Deep GaN through-substrate via etching using Cl2/BCl3 inductively coupled plasma, J. Vac. Sci. Technol. A 38 063003 (2020).

N. Okamoto et al. GaN Through-substrate Via Process for GaN-on-GaN HEMT Power Amplifiers, CS ManTech Conf., May 2021, 6.1.

N. Okamoto et al. SiC Backside Via-hole Process for GaN HEMT MMICs Using High Etch Rate ICP Etching, CS ManTech Conf., ¬May 2009, 7.1.

† N. Okamoto et al. Backside Process

Considerations for Fabricating Millimeter-Wave

GaN HEMT MMICs, CS ManTech Conf.,

May 2010, 15.1.