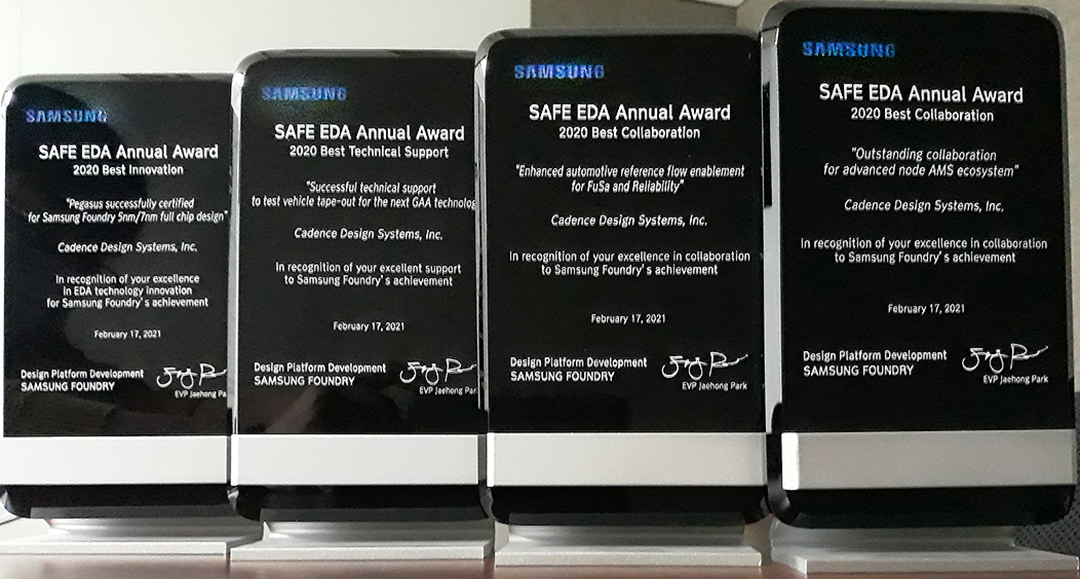

Cadence Wins Four 2020 Samsung Foundry SAFE EDA Awards

Cadence Design Systems, Inc. announced that it has received four 2020 SAFE EDA awards from Samsung Foundry. Cadence garnered a best technical support award for a 3nm test vehicle tapeout for Samsung Foundry’s next-generation gate-all-around (GAA) technology as well as a best innovation award for Samsung Foundry’s 5nm/7nm full-chip design certification of the Cadence Pegasus Verification System. In addition, Cadence won two awards for best collaboration—one for its role in the Samsung Foundry advanced-node analog/mixed-signal (AMS) ecosystem, which is dedicated to 3nm advancement, and the other for delivering a newly enhanced automotive reference flow for functional safety and reliability.

These awards were given to Cadence based on the following work that has been delivered:

3nm test vehicle tapeout for next-generation GAA technology: The Cadence full digital tool suite was used to implement and sign off timing on a 3nm test chip tapeout, demonstrating real silicon data as a proof of concept for advanced-node customers.

Pegasus Verification System 5nm/7nm certification: The Cadence Pegasus Verification System, certified for Samsung Foundry’s 5nm and 7nm process technologies, has been optimized to enable advanced-node customers to reach signoff accuracy and runtime goals in a variety of market areas, including the mobile and hyperscale markets.

3nm AMS enablement: The Cadence custom and AMS IC design flow achieved certification for Samsung Foundry’s 3nm GAA technology, providing mutual customers with access to a highly automated circuit design, layout, integrated signoff and verification flow with unique in-design electrically driven, EM-aware place-and-route custom automation capabilities to efficiently design products for automotive, mobile, data center, artificial intelligence (AI) and other emerging applications. Tools in the flow included the Virtuoso custom IC design platform, the Spectre® Simulation Platform and the Innovus Implementation System.

Automotive reference flow enablement: Cadence optimized its digital full flow for Samsung Foundry’s 14LPU process technology using the Cadence Tensilica® ConnX B10 DSP, enabling automotive designers to quickly deliver accurate first-time silicon, achieve power, performance and area (PPA) goals, and meet functional safety and quality/reliability targets.

“We’ve worked with Cadence to ensure our mutual customers have access to our latest technologies so they can achieve the best possible design results and get to market faster,” said Jaehong Park, executive vice president of Foundry Design Platform Development at Samsung Electronics. “Cadence delivered exemplary innovations last year, and the Samsung Foundry SAFE EDA awards were certainly well deserved.”

“Enabling our customers to achieve design excellence is our top priority, and these awards from Samsung Foundry are indicative of our commitment to working closely with customers to reach their goals,” said Michael Jackson, corporate vice president, R&D in the Digital & Signoff Group at Cadence. “Through our continued collaboration with Samsung Foundry, we’ve successfully delivered new technologies so that customers can create products across a variety of emerging areas, including the automotive, mobile and hyperscale markets.”

Cadence tools and flows are part of the company’s Intelligent System Design strategy, which enables SoC design excellence